## Lab 1: Schematic and Layout of a NAND gate

In lab 1, our objective is to:

- Get familiar with Cadence environment.

- Draw a schematic of a simple NAND gate and simulate it.

- Draw layout of a NAND gate using cell library, design rule check (DRC), extract, layout versus schematic (LVS) and simulate using extracted version.

- Compare these two simulations.

In this lab procedure, detailed procedures and snapshots are given for the shake of understanding. You are supposed to understand the procedures, so that you can design your own circuit later. Following lab procedures will not be elaborated so much except where necessary. Please refer to this lab procedure in future labs as reference.

## Login procedure:

After logging in to the computer in the lab using your existing DoE accounts, double click on "**Sun Systems**" icon to start the remote login server on unix machine. Choose one of the computers from the list and click "**Connect**". If you are unable to connect, click "Setting" and make sure all the checkmarks are ON. Ask TAs for help if you still have trouble. When you are prompted to enter your username and password, ask TAs for username and initial password. Make sure you **change your password** as soon as you log in for the first time and **remember** it for the rest of the labs. *TAs might not be able to help you if you forget your password*.

## **PART A: Procedure**

1) Open a console and create a folder in your home directory for Lab 1 "ELEC4708/lab1"

>mkdir ELEC4708

>cd ELEC4708

>mkdir lab1

>cd lab1

2) **Start Cadence** environment with 0.18 technology file.

>startCds -t cmosp18 -b icfb

3) Close the "What's New" window. You will have "**icfb**" window open.

|                       | icfb – Log: /home/bmorshed/C     | 051095/005109.04 |      | 133 |

|-----------------------|----------------------------------|------------------|------|-----|

| File Tools Options CM | AC Gateway CMOSP18-Documentation |                  | Help |     |

| dsNewsClose()         |                                  |                  |      |     |

|                       |                                  |                  |      |     |

|                       |                                  |                  |      |     |

|                       | Ť.                               |                  |      |     |

| <u>í</u>              | Ť.                               |                  |      |     |

| ouse L                | т.<br>М:                         | R:               |      |     |

4) The next thing we will do is make a library to hold all your work for lab1. Click on Tools -> Library Manager (or simply press F6). Library manager window should pop up.

| Conversion Tool Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---|

| Library Manager 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |   |

| Library Path Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |   |

| Verilog Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |   |

| VHDL Tool Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |   |

| Synopsys Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |   |

| Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |   |

| Constraint Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |   |

| Mixed Signal Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |   |

| Analog Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |   |

| VSdE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |   |

| Technology File Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |   |

| Display Resource Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |   |

| CDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |   |

| AMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |   |

| Camera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |   |

| SKILL Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Log: /home/bmorshed/CDSlogs/CDS.log.64 |   |

| File Tools Options CMC Gateway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CMOSP18-Documentation Help             | 1 |

| t<br>ddsOperLibWanager()<br>t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |   |

| 빈                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |   |

| I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |   |

| mouse L:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |   |

| A second seco |                                        |   |

5) Click File -> New -> Library. Type "lab1" in Name field. Click OK.

| 💻 🛛 Library Manager                        | : Directoryhome/bmorshed/TA/ELEC4708/lab1              |      |

|--------------------------------------------|--------------------------------------------------------|------|

| <u>File E</u> dit <u>Vi</u> ew <u>D</u> es | sign Manager                                           | Help |

| Show Categories                            | Show Files                                             |      |

| Library —                                  | Cell View                                              |      |

| Í                                          |                                                        |      |

| CMCLayoutReference                         |                                                        |      |

| CMCpcells                                  | — New Library                                          |      |

| CMCshare<br>ahdlLib                        | Library                                                |      |

| analogLib                                  | Name lab1                                              |      |

| artisan_io_30<br>artisan sc 30             |                                                        |      |

| basic                                      | Directory                                              |      |

| cdsDefTechLib<br>cmosp18                   |                                                        |      |

| cmosp18_defin_techli                       |                                                        |      |

| lab1<br>package                            |                                                        |      |

| passiveLib                                 |                                                        |      |

| rfExamples<br>tpz973q                      |                                                        |      |

| virage_sram                                | 10me/bmorshed/TA/ELEC4708/labl                         |      |

| vst_n18_sc_tsm_c4                          |                                                        |      |

|                                            | – Design Manager – – – – – – – – – – – – – – – – – – – |      |

|                                            | O Use NONE                                             |      |

|                                            | O Use No DM                                            |      |

|                                            |                                                        |      |

|                                            | OK Apply Cancel Help                                   |      |

| – Messages                                 |                                                        |      |

|                                            | morshed/TA/ELEC4708/lab1/libManager.log.182".          | - IA |

| <u>,</u>                                   |                                                        |      |

|                                            |                                                        |      |

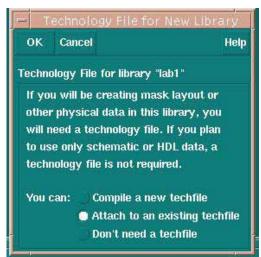

6) Select "Attach to an existing techfile". Click OK.

7) Select "**cmosp18**" from the drop down menu of the Technology Library. Click OK.

| ок | Cancel                   | Defaults | Ap CMCpcells                                                                           | Help |

|----|--------------------------|----------|----------------------------------------------------------------------------------------|------|

|    | iyu Librar<br>gy Library |          | analogLib<br>basic<br>cdsDefTechLib<br>cmosp18                                         |      |

|    |                          |          | cmosp18_defin_techlib<br>package<br>passiveLib<br>rfExamples<br>tpz973g<br>virage_sram |      |

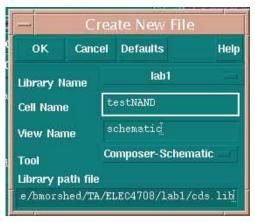

Highlight the new library you have just created, i.e. "lab1", and click File -> New -> Cell View. Type "NAND" in Cell Name. Keep the default values in other fields as shown. Click OK.

| 🛏 Create New File |          |                |         |  |  |

|-------------------|----------|----------------|---------|--|--|

| ОК                | Cancel   | Defaults       | Help    |  |  |

| Library I         | lame     | lab1           |         |  |  |

| Cell Name         |          |                |         |  |  |

| View Na           | me       | schematič      |         |  |  |

| Tool              | C        | Composer-Schen | natic   |  |  |

| Library p         | ath file |                |         |  |  |

| .e/bmors          | hed/TA/I | ELEC4708/lab1/ | cds lib |  |  |

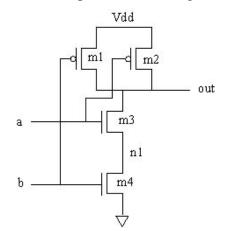

9) A blank **Virtuoso Schemetic Editing** window will open. Move your cursor through the icons on the left side and pop-up descriptions for each will show up. The next thing we

will do is draw the NAND gate using pfet and nfet. We will also add 2 input pins, 1 output pin, 1 VDD pin and 1 GND pin. A circuit diagram of NAND gate is given here.

- 10) To **add an instance** in your schematic, you can click on Instance icon, or click on Add -> Instance, or simply type "**i**" from the keyboard. Add Instance dialog box will show up.

- 11) Click Browse beside Library. Library Manager will pop up.

- 12) In Library, select "**cmosp18**", in cell select "**pfet**", in view select "**symbol**". Then click Close.

| -           |             | Add Instance    |                                                                     |                                                          |                                                   |

|-------------|-------------|-----------------|---------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|

| Hide        | Cancel D    | efaults         | Help                                                                |                                                          |                                                   |

| Library     | cmosp18     |                 | Browse                                                              |                                                          |                                                   |

| Cell        | pfeť        |                 |                                                                     | ary Browser – Add Insta                                  | nce .                                             |

| View        | symbol      |                 | Show Categories                                                     | any provision - Add Insta                                |                                                   |

| Names       | I.          |                 | Library —                                                           |                                                          | - View                                            |

| Array       | Roy         | ws 1 Colum      | ns 1 cmosp18                                                        | pfet                                                     | symbol                                            |

| Rotat       | e           | Sideways        | CMCLayoutReference<br>CMCpcells<br>CMCshare<br>ahdLLib<br>analogLib | netal2_T<br>netal3_T<br>netal4_T<br>netal5_T<br>netal6_T | auLvs<br>hspiceS<br>spectre<br>spectreS<br>symbol |

| lx Use Cell | I           | CMCpcells spcp: | nos artisan_io_30<br>artisan_sc_30                                  | mimcap<br>nfet                                           |                                                   |

| Multiplier  |             |                 | basic<br>cdsDefTechLib                                              | nfet3<br>nfet3 na                                        |                                                   |

| Width       |             | 500. On M       | cmosp18                                                             | nfet_na                                                  |                                                   |

| Length      |             | 180.00n M       | cmosp18_defin_techlib<br>lab1                                       | nfet_rf<br>nlpqlobals                                    |                                                   |

| Drain difi  | fusion area | 0.48u*iPar("w"  | passiveLib                                                          | nmoscap<br>pcapacitor                                    |                                                   |

|             |             | 0 40            | rfExamples<br>tpz973q                                               | pfet<br>pfet3                                            |                                                   |

|             |             |                 | viragejsram<br>vst_n18_sc_tsm_c4                                    | pfet_rf<br>pnp<br>poly1_T<br>resistor<br>sample_rwell    |                                                   |

|             |             |                 | Close                                                               | Filters                                                  | Help                                              |

13) Click Hide and place the instance in your design. You can place multiple instances of same item. When you are done with placing all the instances of that item, press Esc to get rid of it.

14) You can access the **object property** window by selecting a pfet and pressing "**q**". Edit Object Properties window will pop up and will show properties of that instance. You can change length or width if required. For now, we will use defaults widths for pfets and nfets. However, you can change widths later to enhance performance. Note that the default length value is set to the minimum allowed by the technology.

| -                |                      |          | Edi              | t Obji                   | ect Properti        | es     |         |

|------------------|----------------------|----------|------------------|--------------------------|---------------------|--------|---------|

| ок               | Cancel               | Apply    | Default          | s Prev                   | ious Next           |        | Help    |

| Apply<br>Show    | То                   |          | urrent<br>stem 🗖 |                          | ance CDF            |        |         |

|                  | 8                    | rowse    | Re               | set Inst                 | ance Labels Di      | splay  |         |

| Property Value   |                      |          |                  | Display                  |                     |        |         |

|                  | Library Name cmosp18 |          |                  |                          | off                 |        |         |

|                  | Cell Na              | ne:      | pfet             | L.,                      |                     |        | off     |

|                  | View N               | ame      | synd             | olį                      |                     |        | off     |

| Instance Name MI |                      |          |                  |                          | off                 |        |         |

|                  |                      |          |                  | Add                      | Delete              | Modify |         |

|                  | CDF Pa               | ramete   | •                |                          | Value               |        | Display |

| IxUse            | Cell                 |          |                  | CMCpce                   | lls spcpmoš         |        | off     |

| Multip           | lier                 |          |                  | 1                        |                     |        | off 🛁   |

| Width            |                      |          |                  | 500n M                   |                     |        | off     |

| Lengti           | h (                  |          |                  | 180.00n M                |                     | off    |         |

| Drain            | diffusion a          | urea     |                  | 0.48u*iPar("w") <u> </u> |                     | off    |         |

| Sourc            | e diffusior          | ı area   |                  | 0.48u*iPar("w")          |                     | off    |         |

| Drain            | diffusion            | peripher | у                | 0.96u+)                  | 2*iPar("w") M       | E.     | off     |

| Sourc            | e diffusior          | n periph | ery              | 0.96u+                   | 2*iPar("w") M       |        | off 🛁   |

| Drain            | diffusion r          | es squa  | ares             | 0.27u/:                  | iPar ("w") <u> </u> |        | off     |

| Sourc            | e diffusior          | ı res sq | uares            | 0.27u/                   | iPar("w")ľ          |        | off     |

| Drain            | diffusion            | ength    | ĺ                |                          |                     |        | off     |

|                  | e diffusior          |          |                  |                          |                     |        | off     |

- 15) Repeat steps (10) to (14) for "**nfet**"s from the same library and place them in your design.

- 16) To **add pins**, click on Pin from tools button on the left side, or click Add -> Pin, or simply type "**p**" from the keyboard. Add Pin dialog box will open.

- 17) Type the names of the pins you want to add in sequence, leaving a blank space in between. DO NOT click Hide button. You will need to change Direction property for some of the pins.

|                 |               | Add Pin      |            |             |

|-----------------|---------------|--------------|------------|-------------|

| Hide Cance      | el Defaults   |              |            | Help        |

| Pin Names       | A B C VDD GND | [            |            |             |

| Direction       | input 📟       | Bus Expansio | n 🔵 off    | ) on        |

| Usage           | schematic     | Placement    | 🕒 single   | e multiple  |

| Attach Net Expr | ession: 🔵 No  | ).Yes        |            |             |

| Property Name   | L             |              |            |             |

| Default Net Ham | e I           |              |            |             |

| Fout Height     | 0 0685        | Fout Style   | stick      |             |

| Justification   | lowerCenter 🗆 | Entry Style  | fixed off: | set         |

| Rotate          | ş             | lideways     |            | Upside Down |

- 18) Click on the schematic where you want to place pin A. For pin A and B, direction should be **input**, for pin C, direction should be **output**, for pin VDD and GND, direction should be **inputOutput**. Now click "Cancel" of the Add Pin dialog box.

- 19) To **add wires**, click on Wire (narrow) from tools button on the left side, or click Add -> Wire (narrow), or simply type "**w**" from the keyboard. Add Wire dialog box will open.

| -               |        |          | Add Wir | e            |      |

|-----------------|--------|----------|---------|--------------|------|

| Hide            | Cancel | Defaults |         |              | Help |

| Draw M<br>Width | lode [ | route -  |         | Route Method | full |

| Color           |        | cyan     |         |              |      |

| Line Sty        | /le [  | solid    |         |              |      |

- 20) Click hide, and connect the pins with FETs properly to form a NAND gate. Notice that you have to connect the substrate of pfets and nfets properly.

- 21) Click on "**Check and Save**", the first icon on the left hand side toolbar, or click Design > Check and Save, or simply type "X" from the keyboard to save the file.

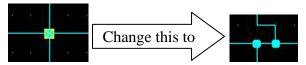

- 22) You might get errors and warnings at this point. Note that Virtuoso will produce warning if a junction has more than 3 wires connected. To avoid this, you can reroute one wire to form 2 junctions instead of 1.

23) Get rid of all errors and warnings. Ask TAs if you need help. Next thing we will do is create a symbol for our NAND gate.

- 24) Click **Design -> Create Cellview -> From Cellview**. "Cellview From Cellview" dialog box will open.

- 25) Keep the default values as shown and click OK.

| OK Cancel De     | efaults Apply |                  |         | He     |

|------------------|---------------|------------------|---------|--------|

| jbrary Name      | lab1]         |                  |         | Browse |

| Cell Name        | NANDĚ         |                  |         |        |

| From View Name   | schematic     | To View Name     | symbolį |        |

|                  |               | Tool / Data Type | symt    | ool —  |

| Display Cellview |               |                  |         |        |

| Edit Options     |               |                  |         |        |

26) Symbol Generation Options dialog box will open. Cut and paste GND from Top Pins field to Bottom Pins field. The dialog box should look like this. Click OK.

| Cell Name | View Name  |

|-----------|------------|

|           |            |

| NANDĚ     | symboli    |

|           | Attributes |

|           | List       |

|           | List       |

|           | List       |

|           | List       |

|           |            |

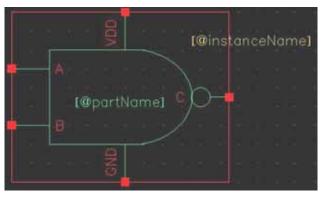

27) Virtuoso Symbol Editing window will open. You can keep the default rectangular shape or change it to your own as you like. To change shape, select and delete rectangular box, click on Line icon in the left side toolbox, select shape and line width as necessary and draw a new shape. You can also move the pins around if you like. This step is optional.

- 28) Save and close the symbol window and schematic window. You will also need to create an **inverter schematic and symbol** using the same procedure (step 8 to 27). Name your inverter as **inv0**. Next we will make a testbench to simulate our NAND gate.

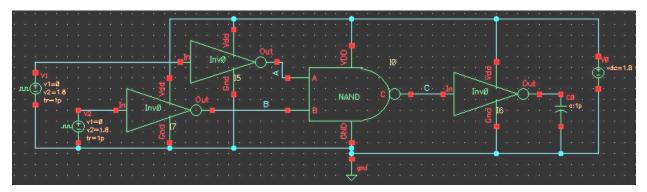

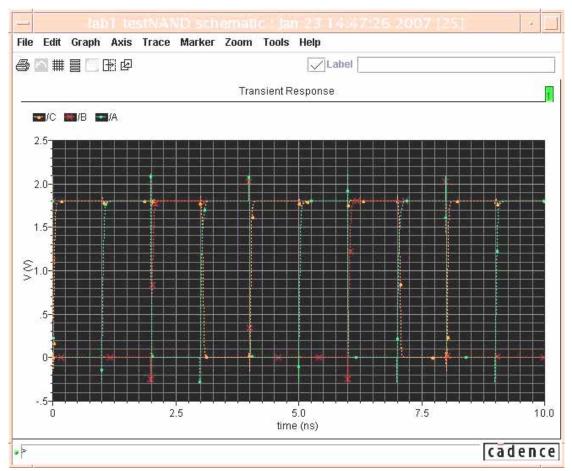

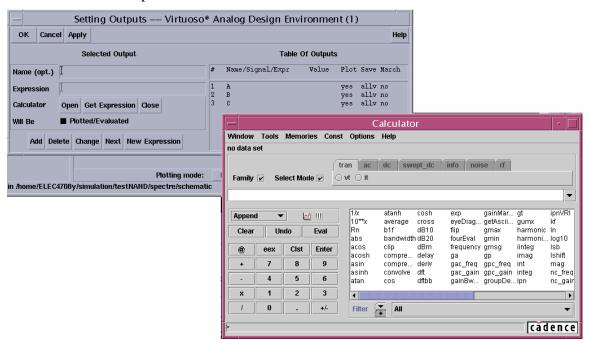

- 29) With "icfb" window highlighted, press F6 to open the library manager. Select lab1 from the library field. Click File -> New -> Cell view. In the Create New File dialog box, enter **testNAND** in the Cell Name field. Keep other default values. Click OK.

30) A blank Virtuoso Schematic Editing window will open. Press "i" to Add Instance. Click Browse. From Library Browser, select lab1 from Library, NAND from Cell, symbol from view. (From now on, this selection sequence will be given as: lab1 -> NAND -> symbol) Click Close. Place the NAND gate in your blank Virtuoso window. Press Esc.

|         | Add Instance    |                                                                                                                                                                                                                                 |                                |         |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------|

| Hide    | Cancel Defaults | Help                                                                                                                                                                                                                            |                                |         |

| Library | Inbl            | Browse                                                                                                                                                                                                                          |                                |         |

| Cell    | KANTÎ           | Hibran                                                                                                                                                                                                                          | Browser - Add Ins              | tance   |

| View    | syaboli         | Show Categories                                                                                                                                                                                                                 | The sectors and a sector store |         |

| Names   |                 | Library                                                                                                                                                                                                                         | Cell                           | Wew.    |

| Amay    | Rows 4 Columns  | lah1<br>CHCLayoutReference                                                                                                                                                                                                      | NAND                           | [sysbol |

| Rotal   | e Sidoways U    | CHCpcells<br>CHCshare<br>whdLibb<br>analogLib<br>artisan_so_30<br>artisan_so_30<br>basic<br>odsDefTechLib<br>tmospl0_defin_techLib<br>HDD<br>package<br>passiveLib<br>cfDramples<br>tpr973p<br>virage_sism<br>vet_n18_sc_tsm_c4 | testhand                       |         |

|         |                 | Oose                                                                                                                                                                                                                            | Filterst.                      | Help    |

31) Press "i" again to Add Instance. Click Browse. From Library Browser, select **analogLib** - > vdc -> symbol. Click Close. Place the "vdc" in your design. Press Esc.

|                                                                    |                  | Ad       | d Instance |                                                                                                                                                                                                                                                      |                                                                                                                                |                                                                                            |

|--------------------------------------------------------------------|------------------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Hide                                                               | Cancel           | Defaults |            | Help                                                                                                                                                                                                                                                 |                                                                                                                                |                                                                                            |

| Library                                                            | analogL          | iĥ       |            | Browse                                                                                                                                                                                                                                               |                                                                                                                                |                                                                                            |

| Cell                                                               | vde              |          |            |                                                                                                                                                                                                                                                      |                                                                                                                                | ng antonin sing sing sing sing sing sing sing s                                            |

| View                                                               | symboli          |          |            | Library                                                                                                                                                                                                                                              | Browser – Ad                                                                                                                   | d Instance                                                                                 |

| Names                                                              |                  |          |            | 🔲 Show Categories                                                                                                                                                                                                                                    | Cell                                                                                                                           | View                                                                                       |

| Array                                                              |                  | Rows 1   | Columns    | janalogLib                                                                                                                                                                                                                                           | vdc                                                                                                                            | jsymbol                                                                                    |

| Rotat<br>AC magn<br>AC phase<br>DC volta<br>Noise file<br>Number ( | itude<br>9<br>ge |          | eways Ups  | CMCLayoutReference<br>CMCpcells<br>CMCshare<br>ahdlLib<br>antisan_io_30<br>artisan_sc_30<br>basic<br>cdsDefTechLib<br>cmosp18<br>cmosp18_defin_techlib<br>lab1<br>package<br>passiveLib<br>rfExamples<br>tp2973g<br>virage_sram<br>vst_n18_sc_tsm_c4 | tline<br>ulwire<br>u2wire<br>u5wire<br>u5wire<br>usernpn<br>vam<br>vcc<br>vcca<br>vcca<br>vcca<br>vccs<br>vccs<br>vccs<br>vccs | A ams<br>auCdl<br>auLvs<br>cdsSpice<br>hspiceD<br>hspiceS<br>spectre<br>spectreS<br>symbol |

|                                                                    |                  |          |            | Close                                                                                                                                                                                                                                                | Filters                                                                                                                        | Help                                                                                       |

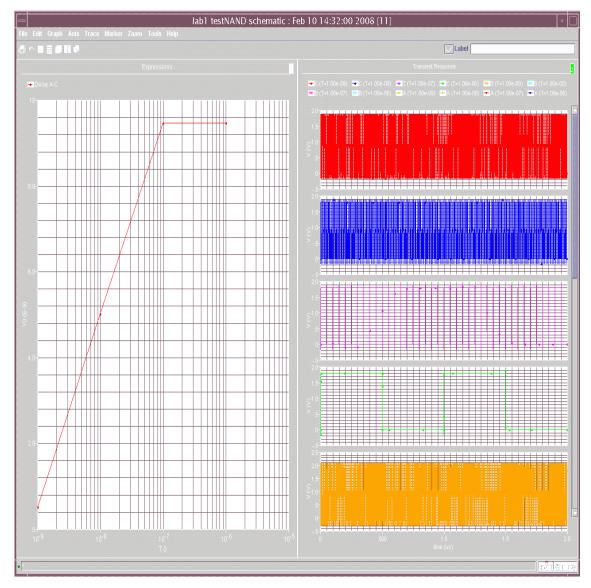

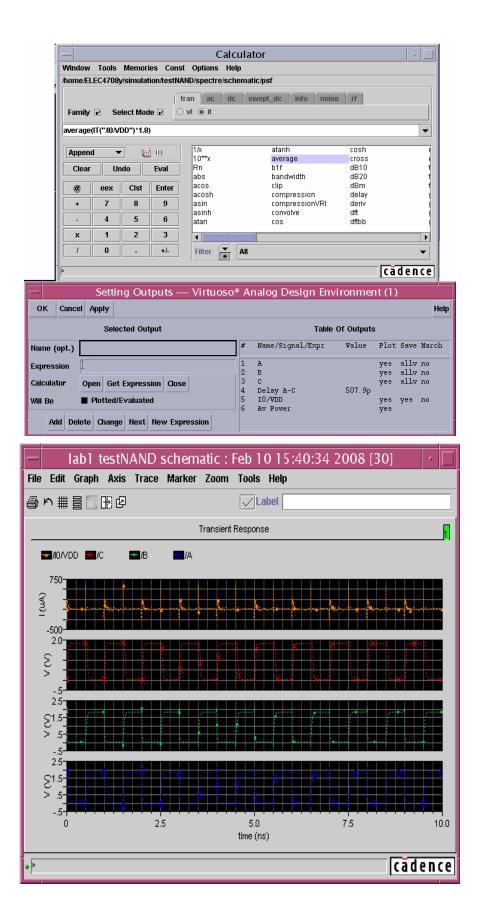

- 32) Press "i" again to Add Instance. Click Browse. From Library Browser, select **analogLib** > **gnd** -> **symbol**. Click Close. Place the "gnd" in your design. Press Esc.