# First Midterm Exam, Fall 2000, October 23

# ELE-461: Microprocessor Systems

# Department of Electronics, Carleton University

| Instructor:        | Maitham Shams             | Name:                            | ·                   |

|--------------------|---------------------------|----------------------------------|---------------------|

| Aids:              | All Allowed               | ID:                              |                     |

| Write your name a  | and ID number on all thr  | ee pages. Attempt all questions. | Exam marks total to |

| 90, so you automat | tically get 10 bonus mark | s for writing the exam! Good luc | ek.                 |

- [1] (4 marks) Microprocessors can only exhibit a limited part of human intelligence. What particular characteristic makes them so useful then? Speed

- [2] (6 marks) What type of memory device is mostly suitable for each of the following.

- a) Small amount of data which is accessed frequently: SRAM

- b) Permanent data for computer set-up: ROM / Flash / EROM

- e) Very large amount of application data: DRAM

- [3] (6 marks) Compatibility between the later and the earlier microprocessors has been a successful strategy for the Intel family. Give two distinct examples of the modifications that demonstrate this compatibility.

- answer 1: Registers extended such that all bytes, wotds, or double words answer 2: Memory modes divided into real and protected. real mode for earlier / P compatibility.

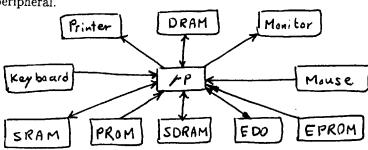

- [4] (10 marks) Draw a simple block diagram of a microprocessor and the following 10 peripherals around it: a keyboard, a printer, a DRAM, a monitor, a mouse, an SRAM, a PROM, an SDRAM, an EDO, and an EPROM. Only and only show the direction of data flow between the microprocessor and each peripheral.

[5] (7 marks) Assume DS=00EF(H). Answer the following questions regarding memory management in the real and protected modes.

DS = 0000 0000 1110 1111

- a) What does DS specify in the real mode? What specifications can you give?

A data Segment in memory. Starts at OOEFO, with 64k limit, ends at

(FFFF) 10EEE

- b) What does DS specify in the protected mode? What specifications can you give?

Selector for descriptors. Selector specifies descriptor number 1D = 29

it is local descriptor with lowest privillege (11).

- [6] (12 marks) The last stored items in the stack are the following hexadecimal values: 08 (very last), FA, 14, 92, 5E, 38, etc. Assume SS=00E0(H) and SP=01CB(H).

- a) What is the physical address of the location containing 08? SSX10 + SP = 00 EOO + 01CB = 00FCB

Specify the following after a POP EAX instruction is executed in the real mode.

- b) Content of EAX: 92 14 FA 08

- c) Content of SS: oofo

- d) Content of SP: OICB + 4 = OICF

- e) Content of the location SP pointing to: 5 E

- f) Physical address SP pointing to: 00 FC6+4 = 00 FCF

- [7] (12 marks) Write a single *logical* instruction for each of the following operations. Note that no other changes should occur.

- a) Set the most significant nibble in AX to 1: OR AX, FOOO

- b) Clear the even-numbered bits in AX to 0:

- c) Invert bits number 0, 5, 10, and 15 in AX:

- d) Change the sign of the content of AX:

- e) Multiply the content of AX by 16:

- f) Test bit number 5 in AX: TEST AX, 32.

- [8] (6 marks) Write a piece of code to input 150 words of data from a device whose address is PORINP and send it to another device whose address is POROUT.

Need a place in memory for storage, call it "Storage" at its base.

[9] (12 marks) Indicate why each of the following are needed in relation to microprocessors.

- a) Tri-state inverters: For sharing buses

- b) Directives in assembly: To speciff to assembler the size of data (byte, word, e)

- c) Wait states: To enable access / inter face with slower memory / IO.

- d) Buffers at outputs: To drive large loads / Famout.

- e) Bi-directional buffers: For passing data both ways (used with data bus)

- f) Clock signal: For synchronization of different operations / devices.

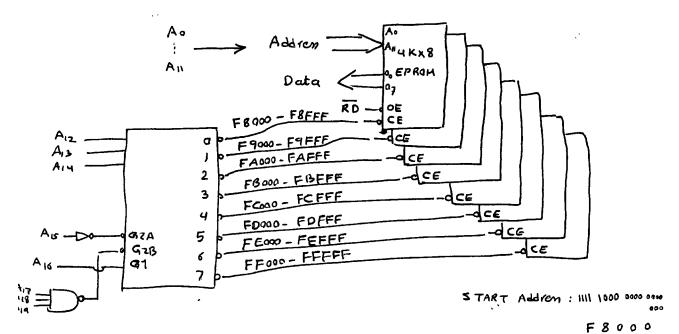

[10] (15 marks) For an 8080 microprocessor (i.e. 20-bit address bus and 8-bit data bus), use the decoder technique to map the upper most 32Kb of memory into eight 4K×8 EPROM chips. Draw the circuit and indicate the start and the end addresses accessible through each EPROM.

Any Negative or Positive Comments

End Addren: FFFF

If you like, you may state any comments or concerns regarding the course, lectures, exam, and labs here. I really appreciate your input.

### Second Midterm Exam, Fall 2000, November 27

### ELE-461: Microprocessor Systems

Department of Electronics, Carleton University

Instructor: Maitham Shams

Aids: All Allowed

Name: Solution

| Write your name and ID number on all three pages. Attempt all questions. You have one hour to write the exam.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| [1] (8 marks) Give two possible reasons for using an interface unit.  (4) a) some peripherals are electromagnetic devices and need signal canversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

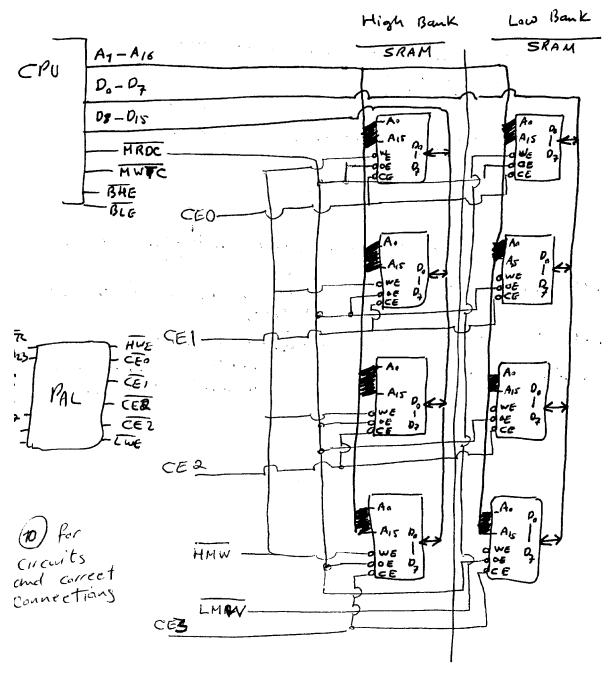

| (4)0) Data transfer rates of pezipherals may be different than CPU.  (C) Data Gode, and formats of peripherals may be different than CPU.  (S) d) operation mode, of peripherals differ from one another and they should not peripherals differ from one another and they should not peripherals differ from one another and interfer each [2] (8 marks) In relation to interfacing a processor to a memory system with more than one bank, other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .t |

| a) Why a separate write control signal is needed for each bank?  (4) To enable CPU to access individual banks for writing data on byte, word, or double-word.  b) Why only one read control signal is needed for all banks?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| O) Why only one read control signal is needed for all banks?  CPU reads anly the portion that it needs from the bus  It may read a byte, a word, or a double word.  [3] (16 marks) Evaluate the Hamming Code parity bits for the following n-bit data and write down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •  |

| the $n + k$ words.  a) 110 $n = 3 \implies k = 3$ $P_1 P_2 D_3 P_4 D_5 D_6$ $P_2 P_3 P_4 D_5 D_6$ $P_3 P_4 P_5 D_6 D_7 P_8 D_8 D_{10} D_{11}$ b) 0110101 $n = 7 \implies k = 4$ $P_1 P_2 D_3 P_4 D_5 D_6 D_7 P_8 D_8 D_{10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| (3,5,7,9,11)=1 (3,6,7)=0 \\  \alpha \begin{align*} \text{P2} = \text{xor} (3,6,7,10,11)=0 \\  \text{Q} \begin{align*} \text{P2} = \text{xor} (3,6,7,10,11)=0 \\  \text{Q} \begin{align*} \text{P3} = \text{xor} (9,14,11)=0 \\  \text{Q} \text{Q} = \text{Xor} (9,14,11)=0 \\  \text{Q} \text{Q} \text{Q} \text{Adjust transfer over synchronous.} \\  \text{Q} \text{Adjust the adjust of technology (5 cales)} \\  \text{Q} \te |    |

| better with af devices af devices we of a wider started with technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ,  |

| [5] (8 marks) Answer the following questions regarding signal bouncing.  (a) What sort of danger it poses? wrong data may be sampled.  (3) b) What is the hardware technique for debouncing? using special switches called debouncing? Switches.  (5) What is the software technique for debouncing? Deland Loop is sention before sampling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

See the back.

input and output signals.

#### Any Negative or Positive Comments

If you like, you may state any comments or concerns regarding the course, lectures, exam, and labs here. I really appreciate your input.