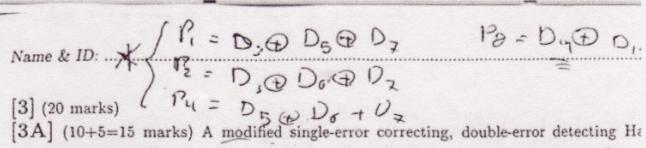

[3A] (10+5=15 marks) A modified single-error correcting, double-error detecting Ha four bits of Data  $D_3$ ,  $D_5$ ,  $D_6$ , and  $D_7$  has the following parity bit equations:  $P_1 = P_2 = D_3 \oplus D_5 \oplus D_7$ ,  $P_4 = D_3 \oplus D_6 \oplus D_7$ , and  $P_8 = D_5 \oplus D_6 \oplus D_7$ .

a) Find the binary values of the four check bits for a single error in each of the eight bit code. Form a table.

|   | code. Form a table.                                              |

|---|------------------------------------------------------------------|

| ( | code. Form a table.  C P. D. |

|   | C1= P2 @ 03 @ 05 @ 07                                            |

| ) | C4= P4 @ 03 @ 06 @ D7 ()                                         |

| ( | C8 = P8 ⊕ D5 ⊕ D6 ⊕ D7                                           |

|   | * /                                                              |

| Bit | 68 | C4 | CZ | C, |       |   |

|-----|----|----|----|----|-------|---|

| 1   | 0  | 0  | 0  | 1  | 6.5)  |   |

| a   | 0  | 0  | 1  | 0  | (0.5) |   |

| 3   | 0  | 1  | 1  | 1  | 0     |   |

| 4   |    | )  | 0  | 0  | (0.5) |   |

| 5   | 1  | 0  | 1  | 1  | 0     |   |

| 6   | 1  | 1  | 0  | 1  | 0     |   |

| 7   | 1  | 1  | 1  | 0  | 0     |   |

| 1 8 | 1  | ^  | ^  | Λ  | 73    | - |

P. P. D. P. D. D. D. 18

b) For each of the following words read from memory evaluate the check bits and indicate error, double error, or no error has occured. Write the correct word were possible.

i) 101000112

C8 C4 C2 C1 = 0000 => No error (1)

ii) 110<u>0</u>1110

C8 C4 C2 C1 = 1017 => error in bit 50

Right word is: 110 00110

iii) 00011101

C8 C4 C2 C1 = 10 10 => double error (1)

Since it is not in the above.

[3B] (3 marks) What are the limitations of the following techniques for detecting and in memory systems?

a) Error detection using single parity one bit

b) Error correction using single parity none

Al Description of the state of

Name & ID.

[4] (2+5+4=15 marks) We are interested in two implementations of a machine, one with special floating-point hardware. Both machines have a clock rate of 1000 MHz. Consi with the following mix of operations.

| floating-point multiply | 10%      |

|-------------------------|----------|

| floating-point add      | 15%      |

| floating-point divide   | 5% / ~ / |

| integer instructions    | 70%      |

Machine MFP (Machine with Floating Point) has floating point hardware and can the the floating point instructions directly. It requires the following number of clock cycles for class.

floating-point multiply 6

floating-point add 4

floating-point divide 20

integer instructions 2

Machine MNFP (Machine Without Floating Point) has no floating-point hardware and the floating-point operations using integer instructions. The integer instructions all to The number of integer instructions needed to implement each of the floating-point opera

floating-point multiply 30 floating-point add 20 floating-point divide 50

a) Find the MIPS ratings for both machines. MIPS =  $\frac{Inst\ Count}{Exec\_time.10^6}$  =  $\frac{Inst\ G}{Inst\ G}$ MIPS :  $\frac{Clock\ rate}{CPI\ x\ 10^6}$ CPI for MFP =  $\frac{Io\ x\ 4 + 5 \times 20 + 70 \times 2}{Io\ x\ 100}$  =  $\frac{3.6}{2}$ CPI for MNFP =  $\frac{Io\ x\ 4 + 5 \times 20 + 70 \times 2}{Io\ x\ 100}$  and MIPS for MNFP =  $\frac{Io\ x\ 4 + 5 \times 20 + 70 \times 2}{Io\ x\ 100}$ b) If the machine MFP needs 300 million instructions for this program, how many intege

Instruction Class | Frequency on MFP | Count on MFP x106 | Count o

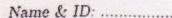

[5] (20 marks) A computer system with an 80386SX microprocessor (24-bit address bubbus) requires 4 Mb of memory starting at address  $0_H$ . This 4 Mb should be divided into at the bottom, 2.0 Mb of DRAM at the middle, and 0.5 Mb of EPROM at the top. The are 64K×8 EPROM chips, 128K×8 SRAM chips, 512K×4 DRAM chips, 3×8 decoder and combinational logic gates. The processor provides MRDC, MWTC, BHE, and BLE signals. The SRAM and DRAM chips have WE, OE, and CE control inputs. The EPRO and CE control inputs. Find the start and end addresses for the three memory parts, drawn and CE control inputs. Find the start and end addresses for the three memory parts, drawn and CE control inputs.

Name & ID: ..

[6] (20 marks)

[6A] (10 marks) A program repeatedly performs a three-step process: It reads in a 4 Kb disk, does some processing on that data, and then writes out the result as another 4 K on the disk. Each block is located on a single track on the disk. The disk rotates at 5 average seek time of 8 ms, and has a transfer rate of 20 Mb/sec. The controller overhead program is using the disk or processor, and there is no overlapping of disk operation wit processing step takes 20 million clock cycles, and the clock rate is 400 MHz. What is the speed of the system in blocks processed per second.

Average rotation time = 0.5 rotations = 5.56 rotations

Transfer time = 4 kb minute 60 seconds

20 Mb/sec = 0.2 ms 2

Average disk access time = 8 ms + 5.56 ms + 0.2 ms + 2

Since each block processed invalues two accesses (read disk component of time is 2×15.76 = 31.52 ms 1)

Computation takes 20 million cycles ×1/400 MHZ = 50 ms

Thus, total time to process one black is 50 + 31.51

Number of black processed per second is

1/0.08152 = 12.27 1

[6B] (6 marks) For the following set of variables, {CPI, clock rate (F), cycle time (T), instructions in program (I), number of cycles in program (C)}, identify all of the subsets to calculate execution time. Each subset should be minimal; that is, it should not conthat is not needed.

- a) F, C

- b) T, C (1.

- c) MIPS, I ()

d) CPI, C, MIPS ()

- e) CPI , I, F

- f) CPI, I, T O