#### **Microprocessor Systems**

#### 97.461

**Maitham Shams**

**Course Slide Presentations**

Department of Electronics Carleton University

# History of Computation

- Mechanical Age: B.C. to 1800s

- 500 B.C. Babylonians invented abacus, first mechanical calculator

- 1642 Blaise Pascal invented calculator using wheels and gears

- 1823 Charles Babbage created Analytical Engine capable of storing data using punch cards

- Electrical Age: 1800s to 1970s

- Triggered by advent of electric motor (conceived by Faraday)

- Motor driven adding machines based on Pascal's idea

- 1896 Hollerith formed Tabulating Machine Company (Today's IBM)

- 1946 ENIAC (Electronics Numerical Integrator and Calculator First general purpose programmable electronic machine Used 17000 vacuum tubes, 500 miles of wires, weighed 30 tons. Performed 100K operations/second, programmed by rewiring)

- Integrated Circuits Age: 1960s to present

- Triggered by development of transistor at Bell Labs, 1948

- 1958 IC technology invented by Jack Kibly of Texas Instruments

- 1971 World's first microprocessor, Intel 4004, 4-bit bus 4K 4-bit(nibble) memory, 50 KIPs, 2300 transistors, 10 μm technology

- 1972 first 8-bit μP, Intel 8008, 16K bytes, 50 KIPs

- 1973 Intel 808, 64K bytes, 500 KIPS, 6000 transistors, 6 μm followed by other 8-bit μPs lke Motorola MC6800 (1974) and Z-8

- 1978 Intel 8086, 16-bit µP, 1M bytes, 2.5 MIPs

Used 4-byts instruction cache to speed up execution time

Base for 80286 µP, also 16-bit with 16M bytes

– 1986 Intel 80386, 32-bit μP, 32-bit data and address busses

4G bytes, 16 to 33 MHz, 275000 transistors, 1  $\mu m$

- 1989 Intel 80486, like 80386 with numeric coprocessor. 4G bytes + 8Kb cache, 25 to 50 MHz, 1.2M transistors, 1 and 0.8 μm

- Advancement continues with Intel, AMD, Motorola, and other  $\mu\text{Ps}$

# Reasons Behind µP Technology

- Speed

- Graphics, Numerical Analysis, CAD, and Signal Processing applications

- Convenience

- Large memory, smaller size, and lower weight

- Power Dissipation

- Portable computers and wireless services

- Reliability

- Noise tolerance in adverse environments and temperatures

- Cost

- Get more done for the money

### µP BASED Computer Systems

Dynamic RAM (DRAM) Static RAM (SRAM) Cache Read-Only (ROM) Flash Memory EEPROM 8086 8088 80186 80286 80386 80486 Pentium Pentium Pro Pentium II Printer Hard disk drive Mouse CD-ROM Drive Keyboard Monitor Scanner

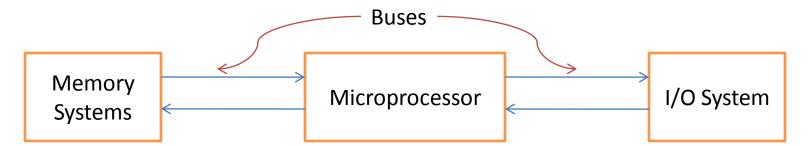

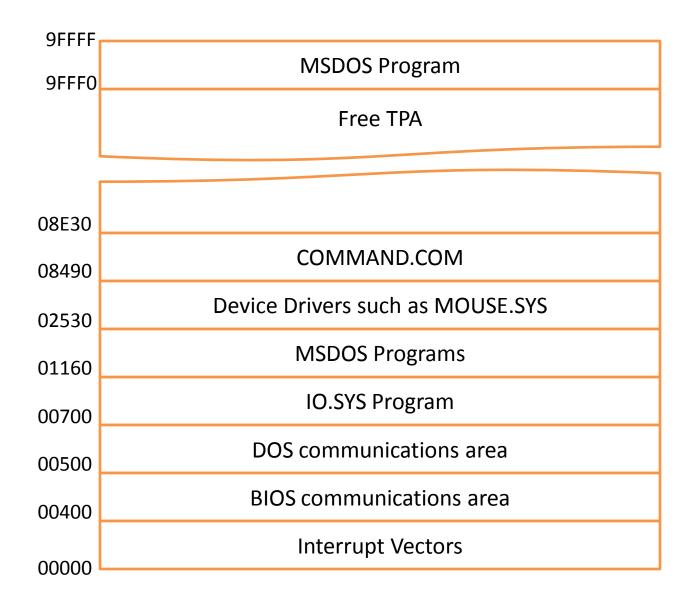

#### Memory

• Transient Program Area (TPA)

- Programs that control computer system (Operating Systems)

- Also contains data, drivers, and application programs

- Consists of RAM, ROM, EEPROM, and Flash Memory

- DOS controls memory organization and some I/O devices

- Interrupt Vectors contain addresses of interrupt service procedures

- BIOS (Basic I/O system) area controls I/O devices

- IO program allows use of keyboard, video display, printer, etc.

- Command program controls operation of computer through keyboard

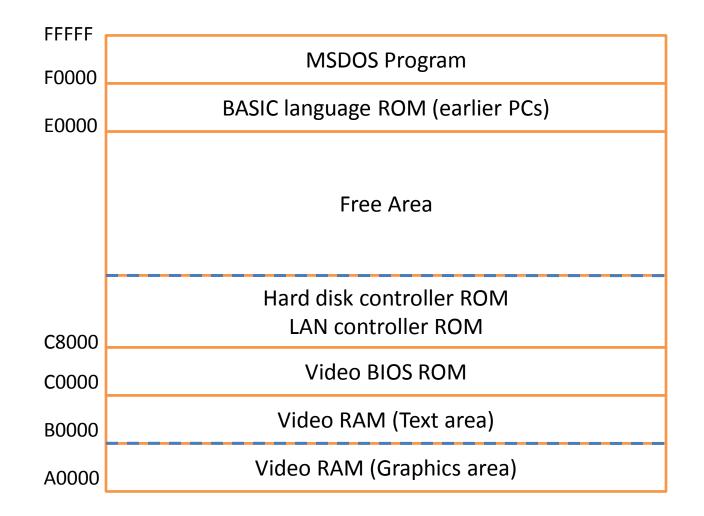

System Area

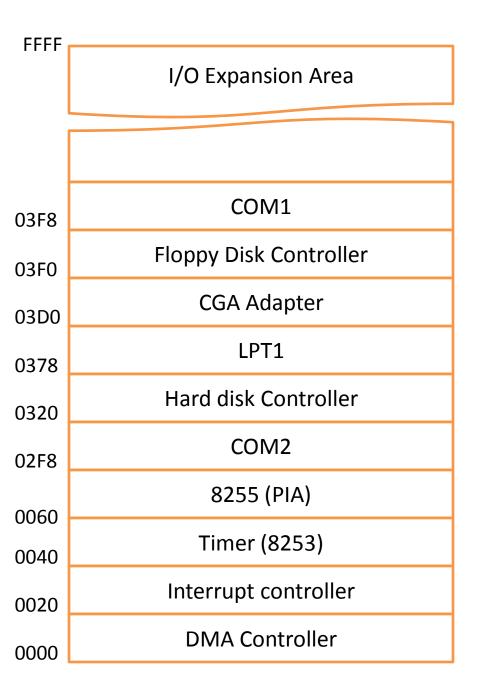

#### • I/O Space

- Addresses I/O ports

- Up to 64K 8-bit devices

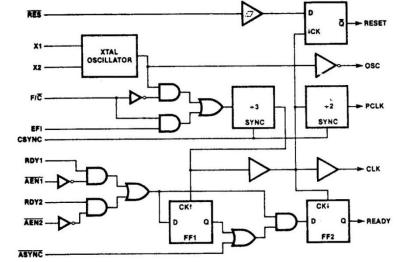

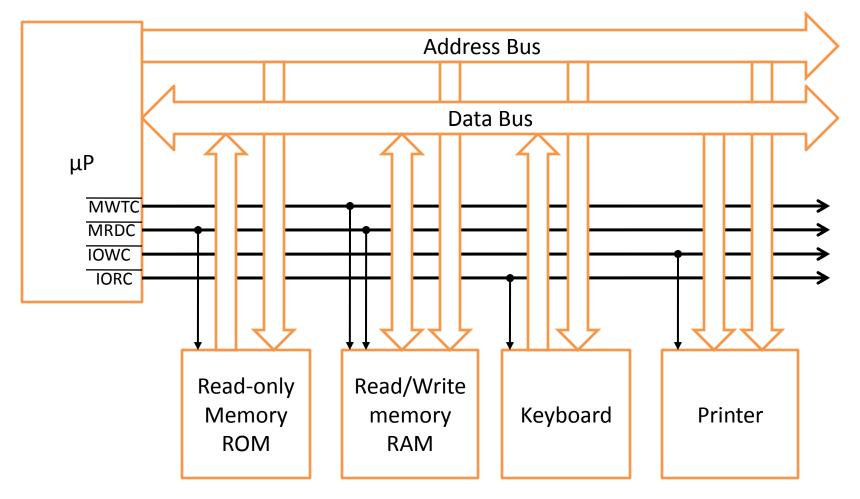

## Microprocessor

- Data transfer between itself and memory or I/O system

- Using data, address, and control buses

- Simple arithmetic and logic operations

- Add, Sub, Mul, Div, AND, OR, NOT, NEG, Shift, Rotate

- Data width: byte (8-bit), word (16-bit), and double word (32-bit)

- Program flow via simple decisions

- Zero, Sign, Carry, Parity, Overflow

- Why is it so important?

## **Computer System Block Diagram**

- Bus is a common group of wires for interconnection

- Address Bus: 16-bit for I/O and 20 to 36-bit for memory

- Data Bus: 8 to 64-bit, the wider the bus, the more data can be transferred

- Control Bs: contains lines that selects the memory or I/O to perform a read or write operation

- Four main control lines

- MRDC' (memory read control)

- MWTC' (memory write control)

- IORC' (I/O read control)

- IOWC' (I/O write control)

## Intel Microprocessor Architecture

- Operation Modes

- Real: uses 1<sup>st</sup> M byte of memory in all versions

- Protected: uses all parts of memory in 80286 and above

- Register Types

- Program Visible: used during application programs

- Program Invisible: not directly addressable, but used by system

- Program Visible Registers

- 4 Data Registers, 4 Pointer/Index Registers, 4-6

Segment Registers, Instruction Pointer, and Flags

|                  |                    | Accumulator | Base index   | Count    | Data                | Stack pointer | Base pointer | Destination index                | Source index |      | Instruction pointer                                                   | Flags                  | Code                              | Data         | Extra     | Stack         |                  |                                      |   |

|------------------|--------------------|-------------|--------------|----------|---------------------|---------------|--------------|----------------------------------|--------------|------|-----------------------------------------------------------------------|------------------------|-----------------------------------|--------------|-----------|---------------|------------------|--------------------------------------|---|

| 8-bit<br>names   |                    | AL          | BL           | CL       | DL                  |               | 1123         | <br>                             |              |      | 2:2-8                                                                 | 8794)                  |                                   |              |           |               |                  |                                      |   |

|                  | 16-bit<br>names    | -X-         | - <u>8</u> - | -ŏ-      | -ă-                 | SP            | ВР           | ā                                | SI           | 1.00 | ₫                                                                     | FLAGS                  | <br>CS                            | DS           | ES        | SS            | FS               | GS                                   |   |

|                  | -                  | AH          | BH           | ъ        | Н                   |               |              |                                  |              | 20   |                                                                       |                        |                                   |              |           |               |                  |                                      |   |

| Special pur pose | For Mul            |             |              |          |                     |               |              |                                  |              |      | 1993)<br>1994<br>1997<br>1997<br>1997<br>1997<br>1997<br>1997<br>1997 |                        | aperation y                       | add ress of  | R         | Heine         | Segment Register | add-Pentium                          |   |

|                  | Holds memory names | off set EAX | Count in EBX | Loop ECX | Used in Muly DivEDX | special reg.  | ~ -          | points co<br>memory location EDI | string ESI   |      | Adresses next                                                         | Code Segment<br>EFLAGS | candition of MP and control its a | ies Starting | Cade Cade | ber a pragram | Additional data  | Additioned segment registers for 326 | ) |

- Compatibility is a successful strategy

- Register A may be used as 8-bit (AH and AL), 16-bit

(AX), and 32-bit (EAX) fir the later Pentium processors

- e.g. ADD AL, AH; ADD DX, CX; ADD ECX, EBX

- Instructions only affect the intended part of a register

- Later  $\mu P$  versions support earlier version codes

- Some registers are Multipurpose, some are Special Purpose

- Segment Registers generate memory addresses

| Nat Used | ID Flag, chuidicates | 6 Virtual Interrupt Pending /<br>6 Virtual Interrupt Flag | B Alignment Check (486SX PP) | Virtual Ma | 0 Resume execution after debugging | F Nested task (software) BI | E Highest = 00, Lawet = 11 B | 12 I/O privilege level | I overflow for signed operation 6 | 5 Direction Plag, For DI/SI register S | © Interrupt flag, enable/disable INTR | » Trap Flag for debugging | L Sign flag, 1= '-', Ø= '+` |                   | result = \$ > 2=1, result \$ \$ > 2=\$ | + Auxiliary carry | halds he carry | N & For odd parity, 1 for even parity | Parity = number of ones | O Holds Carry/borrow & indicates errors |  |

|----------|----------------------|-----------------------------------------------------------|------------------------------|------------|------------------------------------|-----------------------------|------------------------------|------------------------|-----------------------------------|----------------------------------------|---------------------------------------|---------------------------|-----------------------------|-------------------|----------------------------------------|-------------------|----------------|---------------------------------------|-------------------------|-----------------------------------------|--|

|          |                      | VIP VIF                                                   | T                            | VMF        |                                    | NT                          | IOP<br>1                     | IOP<br>0               | 0                                 | D                                      | 1                                     | т                         | S                           | Z                 |                                        | А                 |                | Р                                     |                         | с                                       |  |

|          | -                    |                                                           | •                            | 4          |                                    |                             |                              |                        |                                   |                                        | · · ·                                 |                           | 8                           | ——8<br>038<br>—80 | 3028<br>6/89<br>486                    | 86D               | x              | 38                                    |                         |                                         |  |

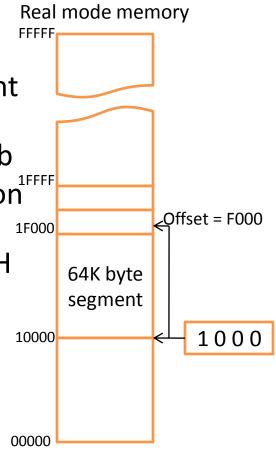

## Real Mode Memory Addressing

- Segment address located in a segment register; always appended with 0H

- Segments always have length of 64 Kb

- Offset or displacement selects location

within 64 Kb of segment

1F000

- e.g. 1000:2000 gives location 12000H

- Default Segment and Address Registers

- e.g. code segment and instruction pointer CS:IP and stack segment and stack pointer SS:SP

CS SS DS H 0001 H of L 200 H ω L Щ N 0 0 4 4 σ 1 1 Stack 0 0 0 Data Code DOS and drivers Memory Stack Code Data 00000 0A480 0A47F 0A0F0 0A0EF 090F0 0908F 0A280 0A27F FFFFF segment overlap Imaginary side view detailing OODO a ta D Sto B to X

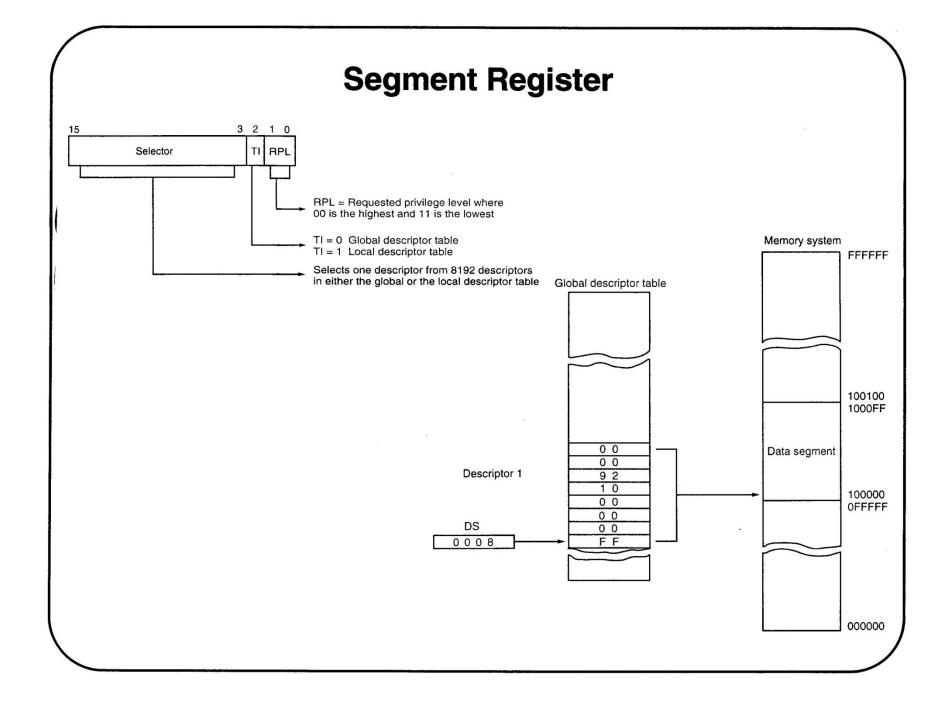

#### Protected Mode Memory Addressing

- Accessed via segment and offset address, but

- Segment register contains a selector

- Selector selects a descriptor from descriptor table

- Descriptor: memory segment location, length, and access right

- Two types of descriptor tables

- Global/system descriptors used for all programs

- Local/application descriptors used for applications

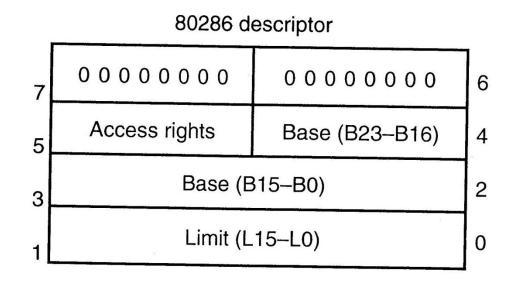

- Each descriptor is 8 bytes

- 16-bit segment register contains 3 parts

- Left most 13 bits address a descriptor

- TI bit access global (0) or local descriptor (1) table

- Right most 2 bits select priority for memory segment access

- How many global and local descriptors in a table?

- How large is a global and a local descriptor table?

- How many memory segments are allowed?

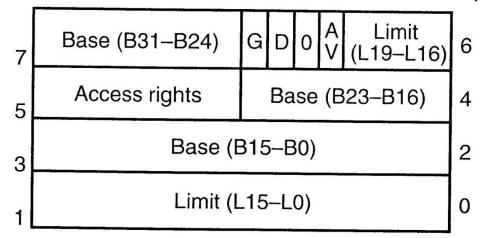

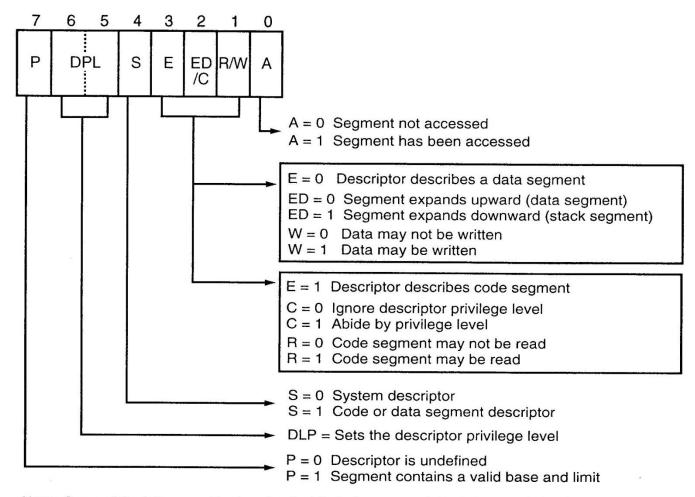

#### **Descriptor Formats**

80386/80486/Pentium/Pentium Pro/Pentium II descriptor

### **Access Right Byte**

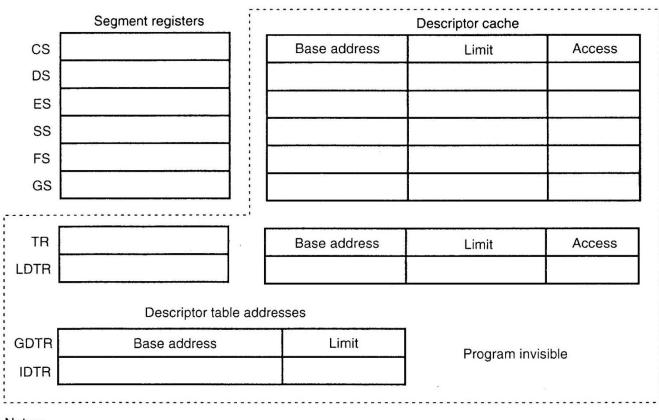

## Program-Invisible Registers

- Each segment register contains a program-invisible portion

- This register is re-loaded when segment register change

- Contains base-address, limit, and access information

- These registers also called descriptor cache

- Other program-invisible registers

- GDTR (global descriptor table register) contain base address and limit for descriptor table

- Location of local descriptor table is selected from global descriptor table using the selector held in LDTR (local descriptor table register)

- Notes:

- 1. The 80286 does not contain FS and GS nor the program-invisible portions of these registers.

- 2. The 80286 contains a base address that is 24-bits and a limit that is 16-bits.

- 3. The 80386/80486/Pentium/Pentium Pro contain a base address that is 32-bits and a limit that is 20-bits.

- 4. The access rights are 8-bits in the 80286 and 12-bits in the 80386/80486/Pentium.

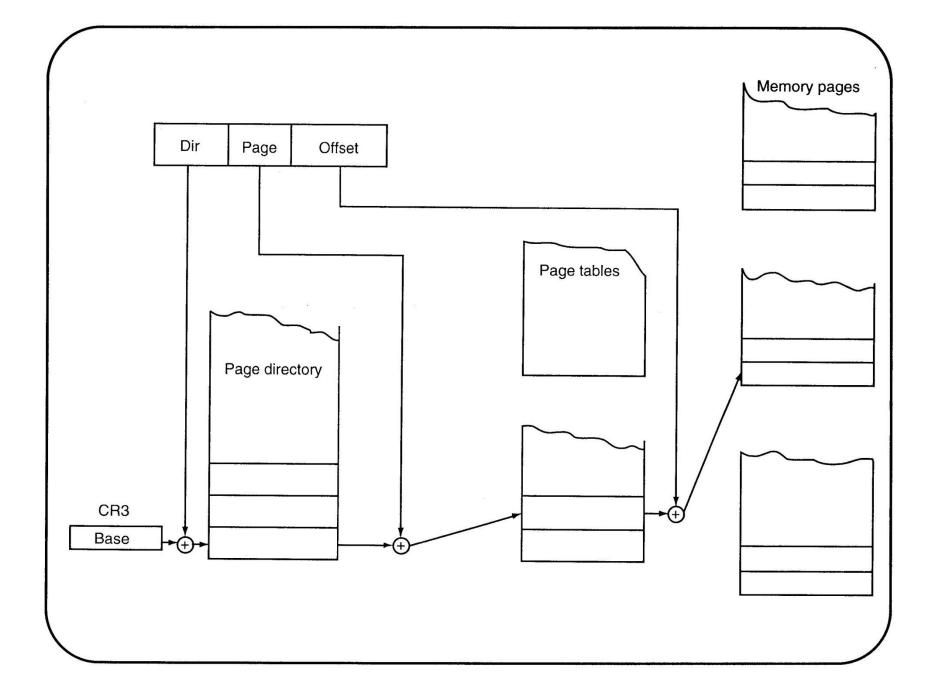

# Memory Paging

- Memory paging changes a linear address to physical

- Linear address is produced by software

- Page directory base is held in a control register (CR3)

- Linear address is broken into 3 sections: directory, page table, offset

- Page directory contains 1024 entries of 4 bytes each which addresses a page table that contains 1024 entries of 4 bytes each

- Each memory page is 4K bytes

- TLB (table look aside buffer) is a cache which contains the 32 most recent page translation addresses

## Addressing Modes

Data Addressing Modes

- Intel family supports 8 data addressing modes

- Modes differ in the location of data and address calculations

- All modes involve physical address generation

- Consider MOV opcode as example: MOV AX, BX

- Opcode or operation code tells  $\mu\text{P}$  which operation to perform

- Source operand is to the right

- Destination operand is to the left

- Register Addressing: MOV CX, DX

- Copy content of source register to destination register

- Source and destination must be of the same size

- Immediate Addressing: MOV AL, 22H

- Transfer the immediate data into destination register

- This is called constant data, but data transferred from a register is a variable data

- Direct Addressing: MOV CX, LIST

- Move a byte or word between a memory location and a register

- Memory address, instead of data, appears in the instruction

- Register Indirect Addressing: MOV AX, [BX]

- Transfer data between a register and a memory location addressed by a register

- Sometimes need using special assembler directives BYTE PTR, WORD PTR, DWORD PTR, when size is not clear

- FOR example MOV DWORD PTR [DI], 10H instead of MOV [DI], 10H

- Base-plus-index Addressing: MOV [BX+DX], CL

- Transfer data between a register and a memory location addressed by a base register and an index register

- Register Relative Addressing: MOV AX, [BX+4]

- Move data between a register and a memory location addressed specified by a register plus a displacement

- Base relative-plus-index Addressing: MOV AX, ARRAY[BX+DI]

- Transfer data between a register and a memory location specified by a base and index register plus a displacement

- Another example is MOV AX, [BX+DI+4]

- Scaled-index Addressing: MOV EDX, [EAX+4\*EBX]

- Address in the second register is modified by a scale factor

- Scale factor are 2, 4, or 8, word, double-word, and quad-word access, respectively

- Only available in 80386 through  $\mu P$

- Other examples: MOV AL, [EBX+ECX] and MOV AL, [2\*EBX]

**Address Generation** Type Instruction Destination Source Register Register Register MOV AX, BX вx ĂX Data Register MOV CH,3AH Immediate **3AH** ČН Memory Register Direct MOV [1234H],AX DS × 10H + DISP address 11234H ÂX 10000H + 1234H Memory Register **Register indirect** MOV [BX],CL  $DS \times 10H + BX$ address CL 10000H + 0300H 10300H Memory address Register SP Base-plus-index MOV [BX+SI],BP  $DS \times 10H + BX + SI$ 10000H + 0300H + 0200H 10500H Memory Register **Register relative** DS × 10H + BX + 4 \_ 10000H + 0300H + 4 MOV CL,[BX+4] address 10304H CL Memory Register MOV ARRAY[BX+SI],DX Base relative-plus-index DS × 10H + ARRAY + BX + SI address ĎX 11500H 10000H + 1000H + 0300H + 0200H 1 Memory Register MOV [EBX+2 × ESI],AX  $DS \times 10H + EBX + 2 \times ESI$ Scaled index address AX 10000H + 00000300H + 00000400H 10700H Notes: EBX = 00000300H, ESI = 00000200H, ARRAY = 1000H, and DS = 1000H

#### Program Memory-Addressing Modes

- Three forms, used with JMP and CALL instructions

- Direct Program Memory Addressing: LMP Label

- Like GOTO or GOSUB in BASIC language

- Allows going to any location in memory for next instruction

- Relative Program Memory Addressing: JMP [2]

- Jump relative to instruction pointer (IP)

- Indirect Program Memory Addressing: JMP AX

- Jump to current code segment location addressed by content of AX

- Other examples: JMP [DI+2[] and JMP [BX]

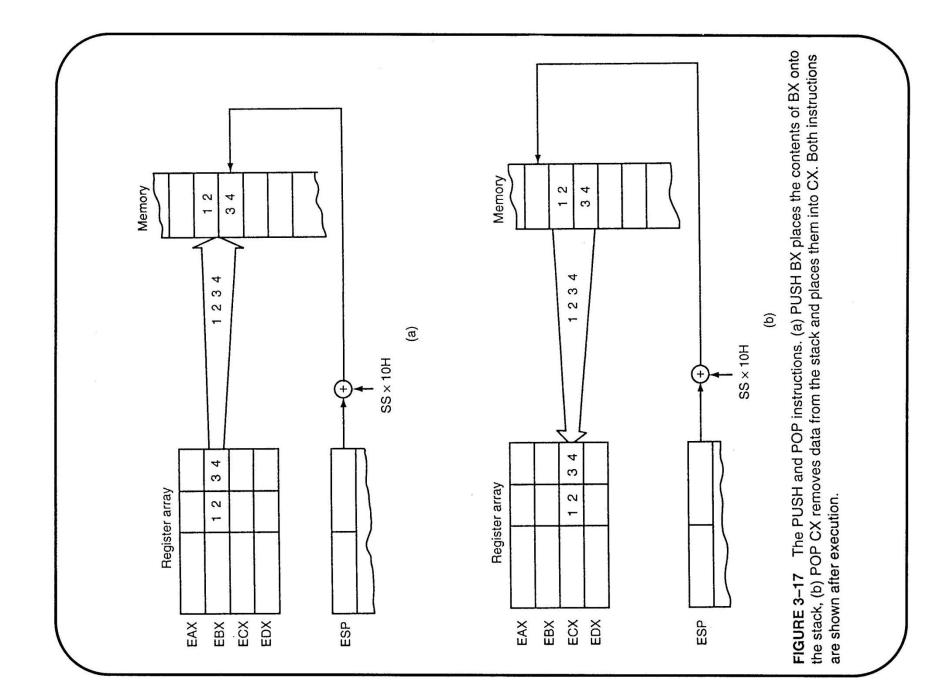

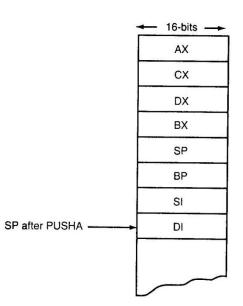

## Stack Memory-Addressing Modes

- Stack is a LIFO (last-in, first-out memory)

- Data are place by PUSH and removed by POP

- Stack memory is maintained by stack segment register (ss) and stack pointer (sp)

- When a word is pushed, high 8 bits are stored at SP-1

low 8 bits are stored at SP-2, the SP is decremented by

2

- When a word is poped, low 8 bits are removed from location addressed by SP, high 8 bits are removed from location addressed by SP+1, then SP is incremented by 2

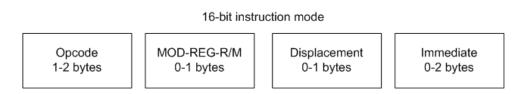

## Instruction Encoding

- Assembler translates assembly code into machine language

- Machine language is the native binary code μP understands

32-bit instruction mode (80386, 80486, Pentium, Pentium Pro, or Pentium II only)

| ,, ,,                     |           |             |              |              |           |

|---------------------------|-----------|-------------|--------------|--------------|-----------|

| Address Size Operand Size | Opcode    | MOD-REG-R/M | Scaled Index | Displacement | Immediate |

| 0-1 bytes 0-1 bytes       | 1-2 bytes | 0-1 bytes   | 0-1 bytes    | 0-4 bytes    | 0-4 bytes |

- Override Prefixes

- First two bytes in 32-bit instructions:

Address size-prefix (67H) and Register size-prefix (66H)

They toggle size of register and operand address from 16-bit to 32-bit or vice versa

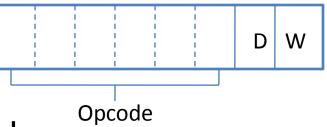

- First byte of instruction: opcode

- First 6 bits of instruction are the binary opcode

- Direction bit (D) determines the direction of data flow

- Width bit (W) determines data size: 0 for byte, 1 for word and double word

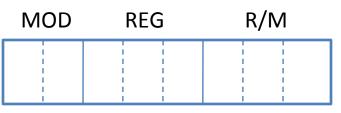

Second byte of instruction: MOD-REG-R/M

- MOD specifies addressing mode for instruction and whether displacement is present

- If MOD=11, then register addressing mode, else memory addressing mod

- In register addressing mode, R/M specifies a register

- In memory addressing mode, R/M selects a mode from table

- If D=1, data flow to REG from R/M, if D=0 data flow to R/M from REG

**TABLE 4–1** MOD field for the 16-bit instruction mode.

Function

00 No displacement

MOD

01 8-bit sign-extended displacement

10 16-bit displacement

11 R/M is a register

**TABLE 4–2**MOD field forthe 32-bit instruction mode(80386–Pentium II only).

| MOD | Function                         |

|-----|----------------------------------|

| 00  | No displacement                  |

| 01  | 8-bit sign-extended displacement |

| 10  | 32-bit displacement              |

| 11  | R/M is a register                |

TABLE 4–3 REG and R/M (when MOD = 11)

assignments.

| Code | W = 0 (Byte) | W = 1 (Word) | W = 1 (Doubleword) |

|------|--------------|--------------|--------------------|

| 000  | AL           | AX           | EAX                |

| 001  | CL           | CX           | ECX                |

| 010  | DL           | DX           | EDX                |

| 011  | BL           | BX           | EBX                |

| 100  | AH           | SP           | ESP                |

| 101  | СН           | BP           | EBP                |

| 110  | DH           | SI           | ESI                |

| 111  | BH           | DI           | EDI                |

TABLE 4-4 16-bit R/M memory-addressing modes.

| R/M Code | Addressing Mode                                                                                                  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------|--|--|

| 000      | DS:[BX+SI]                                                                                                       |  |  |

| 001      | DS:[BX+DI]                                                                                                       |  |  |

| 010      | SS:[BP+SI]                                                                                                       |  |  |

| 011      | SS:{BP+DI]                                                                                                       |  |  |

| 100      | DS:[SI]                                                                                                          |  |  |

| 101      | DS:[DI]                                                                                                          |  |  |

| 110      | SS:[BP]*                                                                                                         |  |  |

| 111      | DS:[BX]                                                                                                          |  |  |

|          | and the second |  |  |

\*Note: See text section, Special Addressing Mode.

TABLE 4-5 32-bit addressing modes selected by R/M.

| R/M Code | Function               |

|----------|------------------------|

| 000      | DS:[EAX]               |

| 001      | DS:[ECX[               |

| 010      | DS:[EDX]               |

| 011      | DS:[EBX]               |

| 100      | Uses scaled-index byte |

| 101      | SS:[EBP]*              |

| 110      | DS:[ESI]               |

| 111      | DS:[EDI]               |

\*Note: See text section, Special Addressing Mode.

#### TABLE 4-6 Segment register selection.

| Code | Segment Register |

|------|------------------|

| 000  | ES               |

| 001  | CS*              |

| 010  | SS               |

| 011  | DS               |

| 100  | FS               |

| 101  | GS               |

\*Note: MOV CS,R/M(16) and POP CS are not allowed by the microprocessor. The FS and GS segments are only avail-able to the 80386–Pentium II microprocessors.

#### FIGURE 4-8 The scaledindex

| ЭX | byte. |  |

|----|-------|--|

| ЭX | byte. |  |

| S S                             | Index | Base |

|---------------------------------|-------|------|

|                                 |       |      |

| ss<br>00 = × 1<br>01 = × 2      |       |      |

| $10 = \times 4$ $11 = \times 8$ |       |      |

### **Examples**

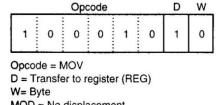

|   |       | Ор    | co | de |       |   | D | • | W | N | IOD |   | F | REG |   |   | R/ | M |

|---|-------|-------|----|----|-------|---|---|---|---|---|-----|---|---|-----|---|---|----|---|

| 1 | <br>0 | <br>0 |    | 0  | <br>1 | 0 | 1 |   | 1 | 1 | 1   | 1 |   | 0   | 1 | 1 | 0  |   |

D = Transfer to register (REG) W = WordMOD = R/M is a register REG = BP R/M = SP

FIGURE 4-4 The 8BEC instruction placed into Byte 1 and 2 formats from Figures 4–2 and 4–3. This instruction is a MOV BP,SP.

| MOD | REG   | R/M   |

|-----|-------|-------|

| 0 0 | 0 1 0 | 1 0 1 |

0 0

MOD = No displacement REG = DL R/M = DS:[DI]

# Intel Family Instruction Set

- PUSH and POP for stack operations

- Load Effective Address

- LEA loads a 16- or 32-bit register with offset address

- LDS, LES, LFS, LGS, and LSS load a 16- or 32-bit register with offset address and a corresponding segment register DS, ES, FS, GS, or SS with a segment address

- String Data Transfer

- Uses destination index (DI) and source index (SI) registers

- Two modes: auto-increment (D=0) and auto-decrement (D=1)

- By default DI access data in extra segment and SI in data segment

- LODS loads AL, AX, or EAX with data addressed by SI in data segment and increments or decrements SI

- STOS stores AL, AX or EAX at the extra segment addressed by DI and increments or decrements DI

- REPS STOS repeats the instruction the number of times stored in CX, i.e. terminates when CX=0

- MOVS is the only instruction that transfers data between memory locations

- INS transfers data from I/O device into extra segment addressed by DI; I/O address is in DX register

- OUTS transfers data from data segment memory addressed by SI to an I/O device addressed by DX

- For inputting or outputting a block of data INS and OUTS are repeated

- Miscellaneous Data Transfer Instructions

- XCHG exchange contents of a register with any other register or memory location

- IN and OUT instructions perform I/O operations

- Two I/O addressing modes: fixed-port and variable port

- In fixed-port addressing the port address appears in instructions, e.g. when using ROM

- In variable-port addressing I/O address in a register

- MOVSX is move and sign extend; MOVZX is move and zero-extend

- CMOV new to Pentiums moves data only if condition is true; conditions are checked for some prior instruction results

- Segment Override Prefix

- May be added to any instruction to deviate from default segment

- Arithmetic and Logic Instructions

- ADD simply adds two numbers and sets the flags

- ADC adds also the carry flag (C)

- INC adds one to a register or memory location

- SUB subtracts two and sets the flags

- SBB subtract-with-borrow also subtracts (C) from difference

- DEC subtracts one from a register or memory location

- CMP is a subtract that only changes the flag bits; this is normally followed by a conditional jump instruction

- Multiplication can be unsigned (MUL) or signed (IMUL)

- Division can also be unsigned (DIV) or signed (IDIV)

- Basic logic instructions are AND, OR, XOR, NOT

- TEST is like CMP, but for bits zero flag Z=1 if bit is 0 and Z=0 if bit is 1

- TEST performs AND operation, so TEST AL,1 tests the first bit and TEST AL,128 tests the last bit of a byte in AL

- NOT is logical inversion or one's complement

– NEG is arithmetic sign inversion or two's complement

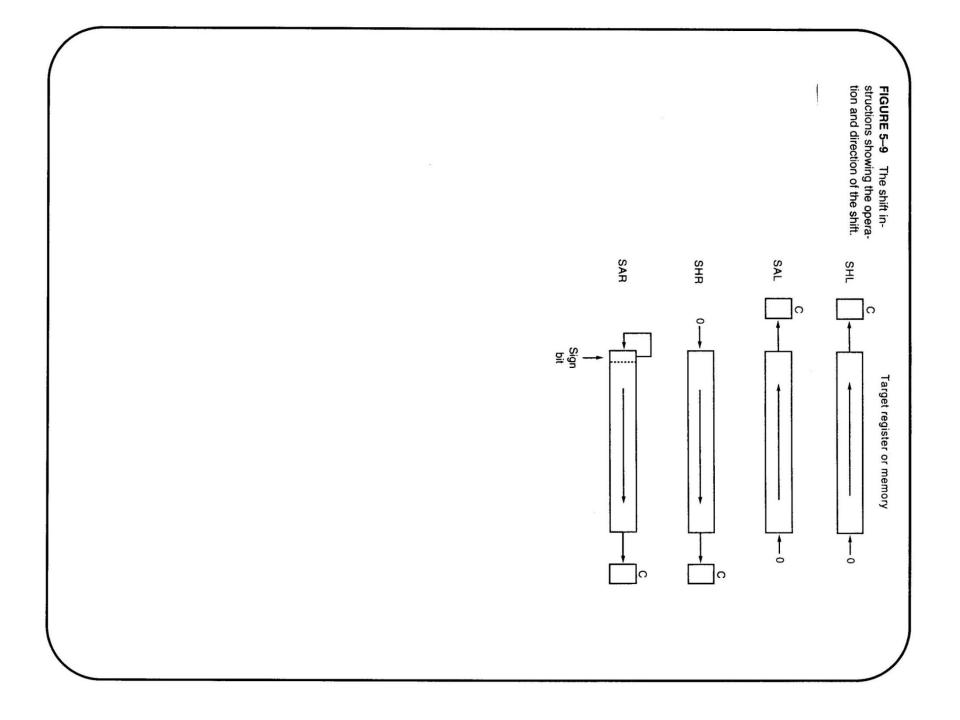

- Shift and Rotate Instructions

- SHL and SHR are logical shift left and right that insert 0 and put one bit in the carry flag C

- SAL and SAR are arithmetic shift operations; SAL is similar to SHL, but SAR is different than SHR because it inserts the sign bit instead of 0

- Rotate instructions rotate data from one end to another, ROL (rotate left) and ROR (rotate right), or through the carry flag (RCL and RCR)

- String Data Comparing

- String scan instruction SCAS compares register A with memory

- Compare string instruction CMPS compares two memory locations

| Symbolic                                                                                                                                                  | Example                                                                                                                                                   | Note                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH reg16<br>PUSH reg32<br>PUSH mem16<br>PUSH mem32<br>PUSH seg<br>PUSH imm8<br>PUSHW imm16<br>PUSHD imm32<br>PUSHA<br>PUSHA<br>PUSHAD<br>PUSHF<br>PUSHF | PUSH BX<br>PUSH EDX<br>PUSH WORD PTR [BX]<br>PUSH DWORD PTR [EBX]<br>PUSH DS<br>PUSH ','<br>PUSHW 1000H<br>PUSHD 20<br>PUSHA<br>PUSHAD<br>PUSHF<br>PUSHFD | 16-bit register<br>32-bit register<br>16-bit pointer<br>32-bit pointer<br>Segment register<br>8-bit immediate<br>16-bit immediate<br>32-bit immediate<br>Save all 16-bit registers<br>Save all 32-bit registers<br>Save flags<br>Save EFLAGs |

4

| Example            | •                                                                                       | Note                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| POPCX              | 16-bit                                                                                  | register                                                                                                                                   |

| POP EBP            | 32-bit                                                                                  | register                                                                                                                                   |

| POP WORD PTR[BX+1] | 16-bit                                                                                  | pointer                                                                                                                                    |

| POP DATA3          | 32-bit                                                                                  | memory address                                                                                                                             |

| POP FS             | Segm                                                                                    | ent register                                                                                                                               |

| POPA               | Pop a                                                                                   | Il 16-bit registers                                                                                                                        |

| POPAD              | Pop a                                                                                   | all 32-bit registers                                                                                                                       |

| POPF               | Pop f                                                                                   | lags                                                                                                                                       |

| POPFD              |                                                                                         | EFLAGs                                                                                                                                     |

|                    | POP CX<br>POP EBP<br>POP WORD PTR[BX+1]<br>POP DATA3<br>POP FS<br>POPA<br>POPAD<br>POPF | POP CX 16-bit<br>POP EBP 32-bit<br>POP WORD PTR[BX+1] 16-bit<br>POP DATA3 32-bit<br>POP FS Segm<br>POPA Pop a<br>POPAD Pop a<br>POPF Pop f |

FIGURE 4–12 The operation of the PUSHA instruction, showing the location and order of stack data. TABLE 4-9 Load-effective address instructions.

| Assembly Language | Operation                                                                      |

|-------------------|--------------------------------------------------------------------------------|

| LEA AX,NUMB       | Loads AX with the address of NUMB                                              |

| LEA EAX,NUMB      | Loads EAX with the address of NUMB                                             |

| LDS DI,LIST       | Loads DS and DI with the 32-bit contents of data segment memory location LIST  |

| LDS EDI,LIST      | Loads DS and EDI with the 48-bit contents of data segment memory location LIST |

| LES BX,CAT        | Loads ES and BX with the 32-bit contents of data segment memory location CAT   |

| LFS DI, DATA1     | Loads FS and DI with the 32-bit contents of data segment memory location DATA1 |

| LGS SI, DATA5     | Loads GS and SI with the 32-bit contents of data segment memory location DATA5 |

| LSS SP,MEM        | Loads SS and SP with the 32-bit contents of memory location MEM                |

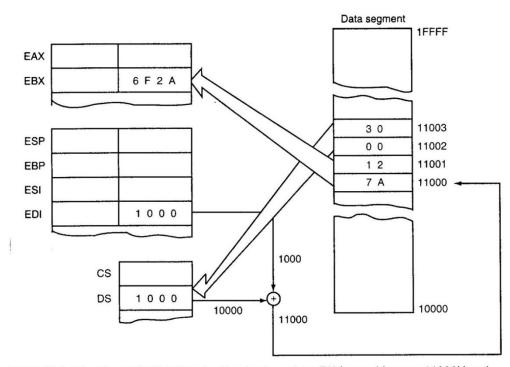

**FIGURE 4–15** The LDS BX,[DI] instruction loads register BX from addresses 11000H and 11001H and register DS from locations 11002H and 11003H. This instruction is shown at the point just before DS changes to 3C00H and BX changes to 127AH.

TABLE 4–10Forms of theLODS instruction.

| Assembly Language                                               | Operation                                                                                                                                                                                                                                                                                          |               |     |                    |              |                  |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|--------------------|--------------|------------------|

| LODSB<br>LODSW<br>LODSD<br>LODS LIST<br>LODS DATA1<br>LODS FROG | $\begin{array}{l} AL = DS:[SI];  SI = SI \pm \mathbf{\hat{1}} \\ AX = DS:[SI];  SI = SI \pm 2 \\ EAX = DS:[SI];  SI = SI \pm 4 \\ AL = DS:[SI];  SI = SI \pm 1 \ (\text{if LIST} \\ AX = DS:[SI],  SI = SI \pm 2 \ (\text{if DAT} \\ EAX = DS:[SI];  SI = SI \pm 4 \ (\text{if FR} \\ \end{array}$ | A1 is a word) |     |                    | Data segment | 1FFFF            |

| Note: The segment can be<br>LODS ES:DATA4.                      | overridden with a segment override prefix                                                                                                                                                                                                                                                          | x as in       |     |                    |              | ]                |

|                                                                 | EAX                                                                                                                                                                                                                                                                                                | AC            | 3 2 | A 0 3 2            | A 0<br>3 2   | 11001<br>11000 - |

|                                                                 | ESP                                                                                                                                                                                                                                                                                                |               |     |                    |              | ]                |

|                                                                 | EBP                                                                                                                                                                                                                                                                                                |               |     |                    |              |                  |

|                                                                 | ESI                                                                                                                                                                                                                                                                                                | 1 0           | 0 0 | -                  |              |                  |

|                                                                 | EDI                                                                                                                                                                                                                                                                                                |               |     |                    |              | 10000            |

|                                                                 |                                                                                                                                                                                                                                                                                                    | CS<br>DS 1 0  | 0 0 | 1000<br>► (†) 1100 | 00           |                  |

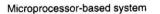

**FIGURE 4–16** The operation of the LODSW instruction if DS = 1000H, D = 0, 11000H = 32, and 11001H = A0. This instruction is shown after AX is loaded from memory, but before SI increments by 2.

TABLE 4–11Forms of theSTOS instruction.

| Assembly Language | Operation                                                 |

|-------------------|-----------------------------------------------------------|

| STOSB             | ES:[DI] = AL; DI = DI ± 1                                 |

| STOSW             | $ES:[DI] = AX; DI = DI \pm 2$                             |

| STOSD             | $ES:[DI] = EAX;  DI = DI \pm 4$                           |

| STOS LIST         | $ES:[DI] = AL; DI = DI \pm 1$ (if list is a byte)         |

| STOS DATA3        | ES:[DI] = AX; DI = DI $\pm 2$ (if DATA3 is a word)        |

| STOS DATA4        | ES:[DI] = EAX; DI = DI $\pm$ 4 (if DATA4 is a doubleword) |

#### TABLE 4-12 Common operand operators.

| Operator | Example          | Comment                                                    |

|----------|------------------|------------------------------------------------------------|

| +        | MOV AL,6+3       | Copies 9 into AL                                           |

| _        | MOV AL,8-2       | Copies 6 into AL                                           |

| *        | MOV AL,4*3       | Copies 12 into AL                                          |

| 1        | MOV AX.12/5      | Copies 2 into AX (remainder is lost)                       |

| MOD      | MOV AX, 12 MOD 7 | Copies 5 into AX (quotient is lost)                        |

| AND      | MOV AX.12 AND 4  | Copies 4 into AX (1100 AND 0100 = 0100)                    |

| OR       | MOV AX,12 OR 1   | Copies 13 into AX (1100 OR 0001 = 1101)                    |

| NOT      | MOV AL,NOT 1     | Copies 254 into AL (0000 0001 NOT equals 1111 1110 or 254) |

#### TABLE 4–13 Forms of the MOVS instruction.

| Assembly Language   | Operation                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------|

| MOVSB               | ES:[DI] = DS:[SI]; DI = DI $\pm$ 1; SI = SI $\pm$ 1 (byte transferred)                     |

| MOVSW               | ES:[DI] = DS:[SI]; DI = DI $\pm 2$ ; SI = SI $\pm 2$ (word transferred)                    |

| MOVSD               | ES:[DI] = DS:[SI]; DI = DI $\pm 4$ ; SI = SI $\pm 4$ (doubleword transferred)              |

| MOVS BYTE1, BYTE2   | ES:[DI] = DS:[SI]; DI = DI $\pm$ 1; SI = SI $\pm$ 1 (if BYTE1 and BYTE2 are bytes)         |

| MOVS WORD1,WORD2    | ES:[DI] = DS:[SI]; DI = DI $\pm 2$ , SI = SI $\pm 2$ (if WORD1 and WORD2 are words)        |

| MOVS DWORD1, DWORD2 | ES:[DI] = DS:[SI]; DI = DI $\pm$ 4; SI = SI $\pm$ 4 (if DWORD1 and DWORD2 are doublewords) |

| TABLE 4–14         Forms of the           INS instruction.         . | Assembly Language                                               | Operation                                                                                                                                                                                  |

|----------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      | INSB                                                            | $ES:[DI] = [DX]; DI = DI \pm 1$ (byte transferred)                                                                                                                                         |

|                                                                      | INSW                                                            | $ES:[DI] = [DX]; DI = DI \pm 2$ (word transferred)                                                                                                                                         |

|                                                                      | INSD                                                            | $ES:[DI] = [DX]; DI = DI \pm 4$ (doubleword transferred)                                                                                                                                   |

|                                                                      | INS LIST                                                        | $ES:[DI] = [DX]; DI = DI \pm 1$ (if LIST is a byte)                                                                                                                                        |

|                                                                      | INS DATA4                                                       | $ES:[DI] = [DX]; DI = DI \pm 2$ (if DATA4 is a word)                                                                                                                                       |

|                                                                      | INS DATA5                                                       | ES:[DI] = [DX]; DI = DI $\pm$ 4 (if DATA5 is a doubleword)                                                                                                                                 |

|                                                                      | <i>Note:</i> [DX] indicates that D<br>available on the 8086/808 | DX contains the I/O device address. These instructions are not 8 microprocessors.                                                                                                          |

| TABLE 4–15 Forms of the OUTS instruction.                            |                                                                 |                                                                                                                                                                                            |

|                                                                      | available on the 8086/808                                       | 8 microprocessors.<br>Operation                                                                                                                                                            |

|                                                                      | available on the 8086/808 Assembly Language                     | 8 microprocessors.<br><i>Operation</i><br>[DX] = DS:[SI]; SI = SI ± 1 (byte transferred)                                                                                                   |

|                                                                      | Available on the 8086/808                                       | 8 microprocessors.<br>Operation                                                                                                                                                            |

|                                                                      | Assembly Language                                               | 8 microprocessors.<br>Operation<br>[DX] = DS:[SI]; SI = SI ± 1 (byte transferred)<br>[DX] = DS:[SI]; SI = SI ± 2 (word transferred)                                                        |

|                                                                      | Assembly Language<br>OUTSB<br>OUTSW<br>OUTSD                    | B microprocessors.<br>Deration<br>[DX] = DS:[SI]; SI = SI ± 1 (byte transferred)<br>[DX] = DS:[SI]; SI = SI ± 2 (word transferred)<br>[DX] = DS:[SI]; SI = SI ± 4 (doubleword transferred) |

Note: [DX] indicates that DX contains the I/O device address. These instructions are not available on the 8086/8088 microprocessors.

#### TABLE 4–16 Forms of the XCHG instruction.

| Operation                                                            |

|----------------------------------------------------------------------|

| Exchanges the contents of AL with CL                                 |

| Exchanges the contents of CX with BP                                 |

| Exchanges the contents of EDX with ESI                               |

| Exchanges the contents of AL with data segment memory location DATA2 |

|                                                                      |

| TABLE 4-17    | IN and OUT |

|---------------|------------|

| instructions. |            |

| Assembly Language | Operation                                  |  |  |

|-------------------|--------------------------------------------|--|--|

| IN AL,p8          | 8-bits are input to AL from I/O port p8    |  |  |

| IN AX,p8          | 16-bits are input to AX from I/O port p8   |  |  |

| IN EAX,p8         | 32-bits are input to EAX from I/O port p8  |  |  |

| IN AL,DX          | 8-bits are input to AL from I/O port DX    |  |  |

| IN AX,DX          | 16-bits are input to AX from I/O port DX   |  |  |

| IN EAX.DX         | 32-bits are input to EAX from I/O port DX  |  |  |

| OUT p8,AL         | 8-bits are output from AL to I/O port p8   |  |  |

| OUT p8,AX         | 16-bits are output from AX to I/O port p8  |  |  |

| OUTp8,EAX         | 32-bits are output from EAX to I/O port p8 |  |  |

| OUT DX,AL         | 8-bits are output from AL to I/O port DX   |  |  |

| OUT DX.AX         | 16-bits are output from AX to I/O port DX  |  |  |

| OUT DX.EAX        | 32-bits are output from EAX to I/O port DX |  |  |

Note: p8 = an 8-bit I/O port number and DX = the 16-bit port address held in DX.

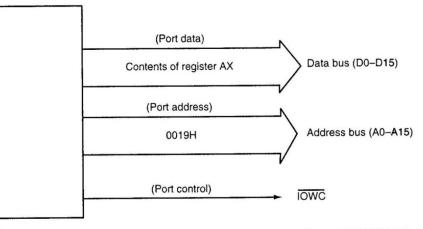

**FIGURE 4–18** The signals found in the microprocessor-based system for an OUT 19H,AX instruction.

| and MOVZX instructions. | Assembly Language | Operation                                                                              |

|-------------------------|-------------------|----------------------------------------------------------------------------------------|

|                         | MOVSX CX,BL       | Sign-extends BL into CX                                                                |

|                         | MOVSX ECX,AX      | Sign-extends AX into ECX                                                               |

|                         | MOVSX BX, DATA1   | Sign-extends the byte at DATA1 into BX                                                 |

|                         | MOVSX EAX,[EDI]   | Sign-extends the word at the data segment memory<br>location addressed by EDI into EAX |

|                         | MOVZX DX,AL       | Zero-extends AL into DX                                                                |

|                         | MOVZX EBP,DI      | Zero-extends DI into EBP                                                               |

|                         | MOVZX DX,DATA2    | Zero-extends the byte at data segment memory<br>location DATA2 into DX                 |

|                         | MOVZX EAX, DATA3  | Zero-extends the word at data segment memory<br>location DATA3 into EAX                |

#### TABLE 4-19 The conditional move instructions.

| Assembly Language | Condition Tested  | Operation                              |                    |                          |                 |

|-------------------|-------------------|----------------------------------------|--------------------|--------------------------|-----------------|

| CMOVB             | C = 1             | Move if below                          |                    |                          |                 |

| CMOVAE            | C = 0             | Move if above or equal                 | 1                  |                          |                 |

| CMOVBE            | Z = 1  or  C = 1  | Move if below or equal                 | TAB                | LE 4–20 Instructions     |                 |

| CMOVA             | Z = 0 and $C = 0$ | Move if above                          | that               | include segment override |                 |

| CMOVE or CMOVZ    | Z = 1             | Move if equal or set if zero           | prefi              | xes.                     |                 |

| CMOVNE or CMOVNZ  | Z = 0             | Move if not equal or set if not zero   |                    |                          |                 |

| CMOVL             | S <> 0            | Move if less than                      | A                  |                          |                 |

| CMOVLE            | Z = 1 or S <> 0   | Move if less than or equal             | Assembly Language  | Segment Accessed         | Default Segment |

| CMOVG             | Z = 0 and $S = 0$ | Move if greater than                   | MOV AX, DS:[BP]    | Data                     | Stack           |

| CMOVGE            | S = 0             | Move if greater than or equal          | MOV AX, ES:[BP]    | Extra                    | Stack           |

| CMOVS             | S = 1             | Move if sign (negative)                | MOV AX,SS:[DI]     | Stack                    | Data            |

| CMOVNS            | S = 0             | Move if no sign (positive)             | MOV AX,CS:LIST     | Code                     | Data            |

| CMOVC             | C = 1             | Move if carry                          | MOV AX, ES:[SI]    | Extra                    | Data            |

| CMOVNC            | C = 0             | Move if no carry                       | LODS ES:DATA1      | Data                     | Extra           |

| CMOVO             | O = 1             | Move if overflow                       | MOV EAX, FS: DATA2 | Data                     | FS              |

| CMOVNO            | O = 0             | Move if no overflow                    | MOV BL, GS: [ECX]  | Data                     | GS              |

| CMOVP or CMOVPE   | P = 1             | Move if parity or set if parity even   |                    | Jula                     | 45              |

| CMOVNP or CMOVPO  | P = 0             | Move if no parity or set if parity odd |                    |                          |                 |

|                      | Operation                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ADD AL, BL           | AL = AL + BL                                                                                                                           |

|                      | CX = CX + DI                                                                                                                           |

| ADD EBP,EAX          | EBP = EBP + EAX                                                                                                                        |

| ADD CL,44H           | CL = CL + 44H                                                                                                                          |

| ADD BX,245FH         | BX = BX + 245FH                                                                                                                        |

| ADD EDX,12345H       | EDX = EDX + 00012345H                                                                                                                  |

| ADD [BX],AL          | AL adds to the contents of the data segment memory location addressed by BX with the sum stored in the same memory location            |

| ADD CL,[BP]          | The byte contents of the stack segment memory location addressed by BP add to CL<br>with the sum stored in CL                          |

| ADD AL,[EBX]         | The byte contents of the data segment memory location addressed by EBX add to AL with the sum stored in AL                             |

| ADD BX,[Si + 2]      | The word contents of the data segment memory location addressed by the sum of SI<br>plus 2 add to BX with the sum stored in BX         |

| ADD CL,TEMP          | The byte contents of the data segment memory location TEMP add to CL with the sum stored in CL                                         |

| ADD BX,TEMP[DI]      | The word contents of the data segment memory location addressed by TEMP plus DI add to BX with the sum stored in BX                    |

| ADD [BX + DI],DL     | DL adds to the contents of the data segment memory location addressed by BX plus DI with the sum stored in the same memory location    |

| ADD BYTE PTR [DI],3  | A 3 adds to the byte contents of the data segment memory location addressed by DI                                                      |

| ADD BX,[EAX + 2*ECX] | The word contents of the data segment memory location addressed by the sum of 2 times ECX plus EAX add to BX with the sum stored in BX |

| TABLE 5-3 Add-       | Add-with-carry instructions.                                                                                                           |

| Assembly Language    | e Operation                                                                                                                            |

| ADC AL,AH            | AL = AL + AH + carry                                                                                                                   |

| ADC CX, BX           | CX = CX + BX + carry                                                                                                                   |

| ADC EBX, EDX         | EBX = EBX + EDX + carry                                                                                                                |

| ADC DH,[BX]          | The byte contents of the data segment memory location addressed by<br>BX add to DH with carry with the sum stored in DH                |

| ADC BX,[BP + 2]      | The word contents of the stack segment memory location addressed<br>by BP plus 2 add to BX with carry with the sum stored in BX        |

| ADC ECX,[EBX]        | The doubleword contents of the data segment memory location addressed by EBX add to ECX with carry with the sum stored in ECX          |

| Assemi<br>INC BL<br>INC SP<br>INC EAX<br>INC BYTI | Assembly Language             | Oneration                                                                                          |

|---------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------|

| INC BL<br>INC SP<br>INC EAX<br>INC BYT            |                               | Aprimius                                                                                           |

| INC SP<br>INC EA<br>INC BYT<br>INC WO             |                               | BL = BL + 1                                                                                        |

| INC EAX<br>INC BYT                                |                               | SP = SP + 1                                                                                        |

| INC BYT                                           |                               | EAX = EAX + 1                                                                                      |

| INC WO                                            | INC BYTE PTR [BX]             | Adds 1 to the byte contents of the data segment memory location addressed by BX                    |

|                                                   | INC WORD PTR [SI]             | Adds 1 to the word contents of the data segment memory location addressed by SI                    |

| INC DW                                            | INC DWORD PTR [ECX]           | Adds 1 to the doubleword contents of the data segment memory location addressed by ECX             |

| INC DATA1                                         | A1                            | Increments the contents of data segment memory location DATA1                                      |

| TABLE 5-4                                         | 5-4 Subtraction instructions. | istructions.                                                                                       |

| Assemt                                            | Assembly Language             | Operation                                                                                          |

| SUB CL, BL                                        | -,BL                          | CL = CL - BL                                                                                       |

| SUB AX,SP                                         | <,SP                          | AX = AX - SP                                                                                       |

| SUB E(                                            | SUB ECX, EBP                  | ECX = ECX – EBP                                                                                    |

| SUB DH,6FH                                        | H,6FH                         | DH = DH – 6FH                                                                                      |

| SUB A)                                            | SUB AX,0CCCCH                 | AX = AX - CCCCH                                                                                    |

| SUB E                                             | SUB ESI,2000300H              | ESI = ESI - 2000300H                                                                               |

| SUB [DI],CH                                       | I),CH                         | Subtracts the contents of CH from the contents of the data segment memory location addressed by DI |

| SUB CH,[BP]                                       | H,[BP]                        | Subtracts the byte contents of the stack segment memory location addressed by BP from CH           |

| SUB A                                             | SUB AH, TEMP                  | Subtracts the byte contents of the data segment memory location TEMP from AH                       |

| SUB DI                                            | SUB DI,TEMP[ESI]              | Subtracts the word contents of the data segment memory location addressed by TEMP plus ESI from DI |

| SUB E                                             | SUB ECX,DATA1                 | Subtracts the doubleword contents of the data segment memory location addressed by DATA1 from ECX  |

| TABLE 5-5                                         | 5-5 Decrement instructions.   | structions.                                                                                        |

| Assen                                             | Assembly Language             | Operation                                                                                          |

| DEC BH                                            |                               | BH = BH - 1                                                                                        |

| DECCX                                             |                               | CX = CX - 1                                                                                        |

| DEC EDX                                           | ×                             | EDX = EDX - 1                                                                                      |

| DECBY                                             | DEC BYTE PTR [DI]             | Subtracts 1 from the byte contents of the data segment memory location addressed by DI             |

| DEC W(                                            | DEC WORD PTR[BP]              | Subtracts 1 from the word contents of the stack segment memory location addressed by BP            |

| DEC DV                                            | DEC DWORD PTR[EBX]            | Subtracts 1 from the doubleword contents of the data segment memory location addressed by EBX      |

| DEC NUMB                                          | MB                            | Subtracts 1 from the contents of the data segment memory location NUMB                             |

| Assembly Language     Corration       CMP CL,BL     CL - BL       CMP EX,SP     XX - SP       CMP EX,SP     XX - SP       CMP FX,SD0H     XX - SP       CMP EX,SD0H     XX - SP       CMP FX,SD0H     XX - SP       CMP FX,SD0H     XX - SP       CMP PX,FIENP     XP experiments from the contents of the data segment memory location addresses by BP subtract from CL.       CMP DI,TEMP[BX]     The word contents of the data segment memory location addresses by SP subtract from AL.       CMP DI,TEMP[BX]     The word contents of the data segment memory location addresses by VP the sum of EDI plus ESI subtract from AL.       CMP DI,TEMP[BX]     The word contents of the data segment memory location addresses by VP the sum of EDI plus ESI subtract from AL.       CMP LI,EDI + ESI     The sum of EDI plus ESI subtract from AL.       CMP LL, EDI + ESI     The sum of EDI plus ESI subtract from AL.       CMP LL, EDI + ESI     The sum of EDI plus ESI subtract from AL.       CMP L, EDI + ESI     AL, EDI + ESI       MUL CL     AL, EDI + ESI       MUL DH     AL is multiplied by PL; the signed product is in AX.       MUL DH     AL is multiplied by PL; the unsigned product is in AX.       MUL DH     AL is multiplied by DF; the unsigned product is in AX. </th <th>TABLE 5-7 Compariso</th> <th>Comparison instructions.</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TABLE 5-7 Compariso | Comparison instructions.                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SL<br>SP<br>SP<br>SP<br>SP<br>CH<br>ESI<br>EDI + ESI<br>EDI + ESI<br>ESI<br>ESI<br>ESI<br>ESI<br>ESI<br>ESI<br>ESI<br>ESI<br>ESI                                                         | Assembly Language   | Operation                                                                                                                                   |

| SP<br>2000H<br>CH<br>CH<br>EMP[BX]<br>EMP[BX]<br>EDI + ESI]<br>EDI + ESI]<br>EDI + ESI]<br>anguage<br>anguage<br>anguage<br>o 32-bit multiplica<br>in ultiplica<br>anguage<br>ABPTR[SI]<br>PTR[SI]<br>PTR[SI]<br>PTR[SI]<br>PTR[SI]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CMP CL,BL           | CL – BL                                                                                                                                     |

| FESI<br>EDI + ESI<br>EDI + ESI<br>EDI + ESI<br>EDI + ESI<br>EDI + ESI<br>EDI + ESI<br>anguage<br>anguage<br>16-bit multiplica<br>16-bit multiplica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CMP AX,SP           | AX – SP                                                                                                                                     |

| 2000H AX<br>CH CH CH<br>EMP[BP] Th<br>EMP[BX] Th<br>EMP[BX] Th<br>by<br>EDI + ESI] by<br>by<br>anguage anguage AX<br>16-bit multiplicatio<br>16-bit multiplicatio<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX<br>AX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CMP EBP, ESI        | EBP – ESI                                                                                                                                   |

| CH<br>EMP[BX]<br>EMP[BX]<br>EDI + ESI]<br>EDI + ESI]<br>EDI + ESI]<br>anguage<br>anguage<br>anguage<br>anguage<br>o 32-bit multiplica<br>'Language<br>'Language<br>'Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMP AX,2000H        | AX – 2000H                                                                                                                                  |

| BPJ Th<br>EMP[BX] by<br>EDI + ESI] by<br>by<br>EDI + ESI] Th<br>by<br>by<br>anguage<br>anguage<br>anguage<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CMP [DI],CH         | CH subtracts from the contents of the data segment memory locatic addressed by DI                                                           |