### Assignment 2

# ELE-350: Digital Electronics

# Department of Electronics, Carleton University

#### Maitham Shams

| Name: | ID: | <br> |

|-------|-----|------|

|       |     |      |

|       |     |      |

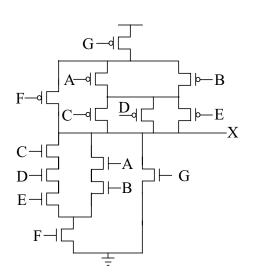

- 1. Implement the equation  $X = ((\overline{A} + \overline{B})(\overline{C} + \overline{D} + \overline{E}) + \overline{F})\overline{G}$  using conventional CMOS technique.

- a. Verify your implementation using Demorgan's theorem. <sup>1</sup>

- b. You realize hat there are more than one way of arranging the transistors for this same fucnition. Suggest as topology (i.e. arrangement or configuration) that gives you the lowest delay and a topology that gives you the highest delay. Explain why in each case. <sup>2</sup>

- c. Size the devices such that the output resistance is the same as that of a inverter with NMOS W/L=1 and PMOS W/L=3.

a)

$$\overline{X} = \overline{((\overline{A} + \overline{B})(\overline{C} + \overline{D} + \overline{E}) + \overline{F})} \overline{G}$$

$$= \overline{((\overline{A} + \overline{B})(\overline{C} + \overline{D} + \overline{E}) + F}) + G$$

$$= \overline{((\overline{A} + \overline{B})(\overline{C} + \overline{D} + \overline{E}) \cdot F}) + G$$

$$= \overline{(\overline{A} + \overline{B} + \overline{C} + \overline{D} + \overline{E})} \cdot F + G$$

$$= \overline{(AB + CDE)} \cdot F + G$$

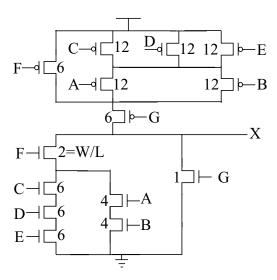

b) Topology (a) gives highest delay because it has highest parasitic capacitance at output. The following topology gives lowest delay, because it only has one PMOS and two NMOS diffusion capacitances at output.

c) In (b) transistors are sized such that any NMOS path has  $(W/L)_{eff}=1$  and any PMOS path has  $(W/L)_{eff}=3$ .

2. Assume that the logic gate of Problem 1 with the "lowest delay" topology is connected of an inverter of size NMOS W/L=1 and PMOS W/L=3. The following data are given.

NMOS transistor data: L=1.2 um,  $V_{TO} = 0.74V$ ,  $k' = 19.6 \times 10^{-6} \text{ A/V}^2$ ,  $\lambda = 0.06 V^{-1}$ ,  $C_{gdo} = 0.43 \text{ fF/um}$ ,  $C_j = 0.3 \text{ fF/um}$ ,  $C_{jsw} = 0.8 \text{ fF/um}$ ,  $t_{ox} = 200 \text{ E-10m}$ , and from layout assume: AD=10u $m^2$ , PD=15um, AS=10u $m^2$ , PS=15um.

PMOS transistor data: L=1.2um,  $V_{TO} = -0.74 V$ ,  $k' = 5.4 \times 10^{-6}$  A/ $V^2$ ,  $\lambda = 0.19 V^{-1}$ ,  $C_{gdo} = 0.43$  fF/um,  $C_j = 0.5$  fF/um,  $C_{jsw} = 0.135$  fF/um,  $t_{ox} = 200$  E-10m, and from layout assume: AD=30u $m^2$ , PD=40um, AS=30u $m^2$ , PS=40um.

General data:  $V_{DD} = 3V$ , all m=0.5 (abrupt junction),  $\phi_0 = 0.6V$ ,  $\varepsilon_{ox} = 3.5$  E-13 F/cm.

- a) Calculate the falling, rising, and average delays from the input of the logic gate to the input of the inverter. Ignore all internal node capacitances and assume that the relevant transistors operate in saturation during transition to  $V_{DD}/2$ . Use the average current formula.

- b) Repeat (a) using the RC delay formula. Are the answers close to those of part (a)?

- c) Calculate the dynamic energy dissipation per cycle. Again ignore the internal capacitances.

Let's first calculate different  $K_{eq}$  values.

|        |      | $V_{High}$ | $V_{Low}$ | K <sub>eq</sub> |

|--------|------|------------|-----------|-----------------|

| H      | NMOS | -1.5       | 0         | 0.697           |

| T<br>L | PMOS | -3         | -1.5      | 0.463           |

|             |      | $V_{High}$ | $V_{Low}$ | K <sub>eq</sub> |

|-------------|------|------------|-----------|-----------------|

| H<br>▼<br>L | NMOS | -3         | -1.5      | 0.463           |

|             | PMOS | -1.5       | 0         | 0.697           |

Note That  $K_{eq}$  for  $(L--->H)_{NMOS} = (H--->L)_{PMOS}$  and  $(H--->L)_{NMOS} = (L--->H)_{PMOS}$ . So , calculating only two values are enough.

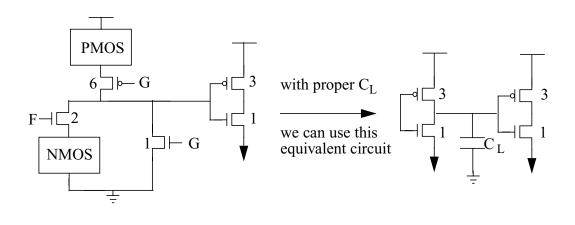

a) The schematic is as follows, where only transistors connected to output are shown, because the problem says ignore internal nodes.

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = 1.75 \text{ fF/u} m^2.$$

$$\overline{C_L = C_{db}|_{(PMOS, W/L=6)} + C_{db}|_{(NMOS \ W/L=1, \ W/L=2)} + C_g|_{(NMOS \ W/L=1, PMOS \ W/L=3)}}$$

$$C_L = K_{eqp} \times (AD_pC_{jn} + PD_pC_{jsw_p}) + K_{eqn} \times (AD_nC_{jn} + PD_nC_{jsw_n}) + Cox(L \times L + L \times 3L)$$

$$C_L = 14.2 + 2 \times 6.95 + 12.6 = 40.70 \, fF$$

## <u>For L--->H</u>

$$CL = Cdb|_{(PMOS~6)} + Cdb|_{(NMOS~1,~2)} + Cg|_{(NMOS~1,~PMOS~3)} = 9.44 + (2)10.46 + 12.6 = 42.96~fF$$

Assuming saturation:

$$I_D = \frac{k'W}{2L}(V_{gs} - V_T)^2 (1 + \lambda V_{DS})$$

# <u>For H--->L</u>

-----

$$I_{\text{NMOS}}(V_{\text{out}}=3V)=\frac{1}{2}(19.6\times10^{-6})(1)(3-0.74)^2(1+0.06\times3)=0.059mA$$

$$I_{\text{NMOS}}(V_{\text{out}}=1.5\text{V}) = \frac{1}{2}(19.6\times10^{-6})(1)(3-0.74)^2(1+0.06\times1.5) = 0.055mA$$

$I_{NMOS}(ave)=0.057mA$

#### For L--->H

$$I_{PMOS}(V_{out}=0V) = \frac{1}{2}(5.4\times10^{-6})(3)(3-0.74)^2(1+0.19\times3) = 0.064mA$$

$$I_{PMOS}(V_{out}=1.5V)=\frac{1}{2}(5.4\times10^{-6})(3)(3-0.74)^2(1+0.19\times1.5)=0.055mA$$

$I_{PMOS}(ave)=0.059mA$

$$t_{phl} = \frac{3 \times 40.7}{2 \times 0.057} = 1.071 ns \; , \; \; t_{plh} = \frac{3 \times 42.96}{2 \times 0.057} = 1.092 ns \; , \; \; \tau_p = \frac{t_{phl} + t_{plh}}{2} = 1.082 ns$$

b)

$$\tau = 0.69RC_{I}$$

For H--->L R=1/2(

$$\frac{V_{DS}}{I}|_{\text{(NMOS, Vout=3V)}} + \frac{V_{DS}}{I}|_{\text{(NMOS, Vout=1.5V)}} = 1/2(\frac{3}{0.059} + \frac{1.5}{0.055}) = 39k$$

$$t_{phl} = 0.69 \times 39 \times 40.70 = 1.095 ns$$

#### For L--->H

R=1/2(

$$\frac{V_{DS}}{I}|_{(PMOS,Vout=0V)} + \frac{V_{DS}}{I}|_{(PMOS,Vout=1.5V)} = 1/2(\frac{3}{0.064} + \frac{1.5}{0.053}) = 37.6k$$

$$t_{plh} = 0.69 \times 37.6 \times 42.96 = 1.114 ns$$

$$\tau_p = \frac{1.095 + 1.114}{2} = 1.1045 ns$$

values are very close!

c) For energy and power calculations, we must calculate C at output when charged from 0--> $V_{DD}$ . Therefore, a different Keq should be used. No miller effect too.

$\text{Keq}|_{\text{(VHigh=-3V, VLOW=0V)}} = 0.58\text{V}.$

(Note that this is average of the two Keq. calculated previously!)

$$C = Cdb|_{(NMOS\ 1,2)} + Cdb|_{(PMOS\ 6)} + Cg|_{(PMOS\ 3)} + Cg|_{(NMOS\ 1)} = 2x8.70 + 11.82 + 12.6 = 41.82\ fF$$

$$E = CV_{DD}^2 = 41.82(3)^2 = 0.376 pJ$$

every/cycle