## Delay of a Digital Gate

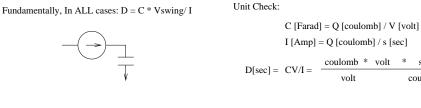

Now then, if only we had a constant current source and a constant capacitance it would be trivial to calculate delay.

coulomb \* volt

volt

sec

coulomb

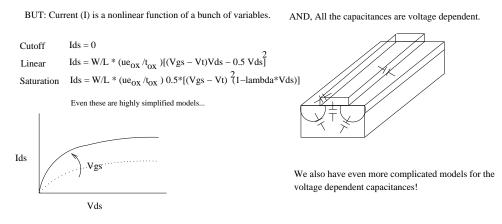

## A SPICE simulator is great for solving all of those detailed equations. We want a simpler way!

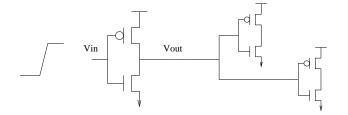

In digital circuits, we are always doing the same thing... Vgs is a step function from 0 to VDD or VDD to 0. What does the output look like?

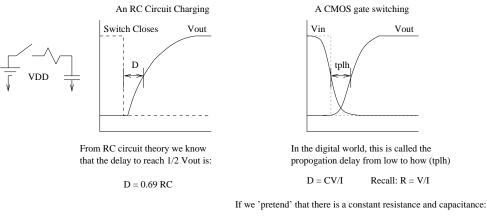

When we simulate it, we get lucky - the output LOOKS A LOT LIKE a resistor charging a constant capacitor !!!

tplh = 0.69 \* Ctotal \* Reffective

So, the question becomes, what are the values for Ctotal and Reffective?

Remember, we introduced these mythical terms to get rid of the complex models. If you REALLY felt the urge you could try to work out Ctotal and Reff but it would be a losing battle. You would need to know the operating mode of the transistors to estimate the instantaneous capacitance and resistance, but the operating modes swing wildly! That's what spice is for.

It is much easier to develop heuristics (rules of thumb) about how the Capacitance and Resistance change with common circuit parameters. You can run a simulation to get the delay (either tphl or tplh), and from there get the effective RC constant of the circuit.