| All inputs used in the procedure must appear in the trigger list<br>Any input change must recalculate the outputs.<br>If no recalculation is done, the old values must be remembered.<br>The synthesizer will insert latches to do this.<br>Things to Include<br><u>Right-hand side variables:</u><br>Except variables both calculated and used in the procedure.<br>always @(a or b or c or xor y)<br>begin<br>x=a; y=b; z=c;<br>w=x+y;<br>end<br>Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>else if (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end |                                     |                  |                     |         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|---------------------|---------|--|

| <pre>If no recalculation is done, the old values must be remembered.<br/>The synthesizer will insert latches to do this.<br/>Things to Include<br/>Right-hand side variables:<br/>Except variables both calculated and used in the procedure.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                         | All inputs used in the proced       | ure must         | appear in the trigg | er list |  |

| Right-hand side variables:<br>Except variables both calculated and used in the procedure.<br>always @(a or b or c or x or y)<br>begin<br>x=a; y=b; z=c;<br>w=x+y;<br>end<br>Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                         | If no recalculation is done, the ol | Id values m      | ust be remembered.  |         |  |

| Except variables both calculated and used in the procedure.<br>always @(a or b or c or xor y)<br>begin<br>x=a; y=b; z=c;<br>w=x+y;<br>end<br>Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                        | hings to Include                    |                  |                     |         |  |

| <pre>always @(a or b or c or x or y)<br/>begin<br/>x=a; y=b; z=c;<br/>w=x+y;<br/>end<br/>Branch controlling variables<br/>The controlling variable for every if and case.<br/>always @(r or s)<br/>begin<br/>if (r) begin x=2; y=0; z=0; end<br/>elseif (s) begin x=0; y=3; z=0; end<br/>else begin x=0; y=0; z=4; end</pre>                                                                                                                                                                                                                                                                                                                                                | <u>Right-hand side variables:</u>   |                  |                     |         |  |

| <pre>begin</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Except variables both calculated a  | and used in      | the procedure.      |         |  |

| <pre>begin</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | always @(a or b or c or x           | <del>or v)</del> |                     |         |  |

| w=x+y;<br>end<br>Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     | • •              |                     |         |  |

| end<br>Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                                                                                                                                                              | x=a; y=b; z=c;                      |                  |                     |         |  |

| Branch controlling variables<br>The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.                                  |                  |                     |         |  |

| The controlling variable for every if and case.<br>always @(r or s)<br>begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | end                                 |                  |                     |         |  |

| <pre>always @(r or s)     begin     if (r)    begin    x=2; y=0; z=0; end     elseif (s)    begin    x=0; y=3; z=0; end     else    begin    x=0; y=0; z=4; end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Branch controlling variables        |                  |                     |         |  |

| <pre>always @(r or s)     begin     if (r)    begin    x=2; y=0; z=0; end     elseif (s)    begin    x=0; y=3; z=0; end     else    begin    x=0; y=0; z=4; end</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | The controlling variable for eve    | rv if and        | case.               |         |  |

| begin<br>if (r) begin x=2; y=0; z=0; end<br>elseif (s) begin x=0; y=3; z=0; end<br>else begin x=0; y=0; z=4; end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U                                   | •                |                     |         |  |

| elseif (s) begin $x=0; y=3; z=0;$ end<br>else begin $x=0; y=0; z=4;$ end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - · · · ·                           |                  |                     |         |  |

| else begin $x=0; y=0; z=4;$ end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |                  |                     |         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |                  |                     |         |  |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | else                                | begin            | x=0; y=0; z=4;      | end     |  |

### Writing Procedural Code Without Latches

# Writing Procedural Code Without Latches II

### Eliminating Latches

Let the inputs to a combinational logic block be held by latches, flip flops, or by input switches. Then the outputs only change if an input(s) change.

Moreover variables thought of as control variables are just as much inputs as those thought of as data.

### Re-evaluation must be done if any input changes

The trigger list (event list) controls when the procedure is evaluated. This must contain all input variables.

### <u>Inputs</u>

Data Inputs:

All inputs which appear on the right hand side in any operation.

However if they appear on both the right and left sides of expression, they are not included because the variable changing inside the loop would retrigger the loop. This could cause infinite zero-delay loops. It is hard to think of a legitimate synthesizable concept using a procedure that retriggers itself.

### Control inputs

Any variable checked by the control of an *if* or *case* statement. Other procedural operators do not cause branches or are not synthesizable.

11.• PROBLEM What latches, if any will be generated?

always@ (z or x)

if (z==1) w=x; else w=~v;

More problems on next page.

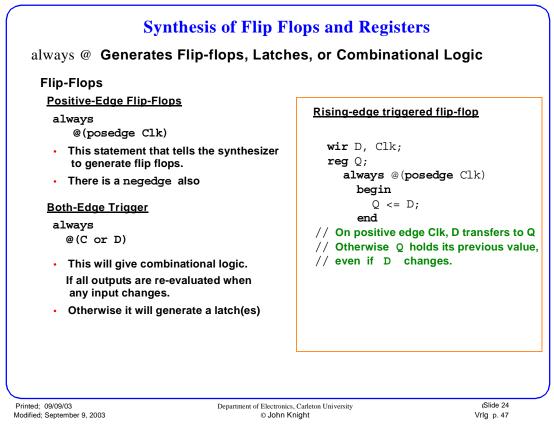

### Synthesis of Flip-flops -

Writing Procedural Code Without Latches

# **Synthesis of Flip-flops**

### always @(posedge clk)

### The synthesizer interprets this to mean flip flop(s)

This command, and only this command (or always@(negedge clk) ) gives a flip-flop or a register of flip-flops.

### 12.• MORE PROBLEMS ON GENERATING UNWANTED LATCHES

Are any signals latched in the following code? Which ones?

a) always@(aziz or bob or chu)

case (aziz)

2'b00 : z=bob;

2'b01 : z=chu;

2'b11 : y=bob & chu;

2'b10 : y=bob | chu;

endcase

b) always @(a or b or c) begin

if (c) begin x=a; y=b; end else y=b+x;

x=3'd6; // Never mind that this makes x=a redundant, the point is do we generate latches.

end

Writing Procedural Code Without Latches

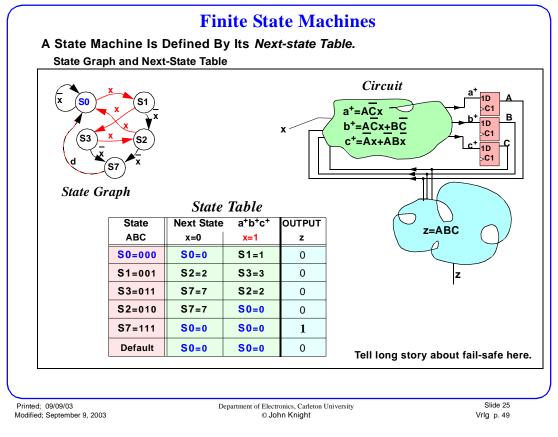

# Finite-State Machines (FSMs)

This is a model for many circuits. For example counters are FSMs with no inputs.

### <u>State</u>

The state is the collective contents of all the flip-flops (latches).

A state machine is described by

- a. Its states and a description of their physical meaning.

- The way the machine makes transitions to the next state. These must be based on the present state and the present inputs only.

- c. The outputs from each state.

#### **Outputs**

- Moore Outputs: These may depend only on the state flip-flops. Moore machines are easier to design and <u>can</u> give glitch free outputs.

- b. Mealy outputs depend on the flip-flops and/or on the inputs directly. Mealy machines usually have fewer states and thus are often smaller.

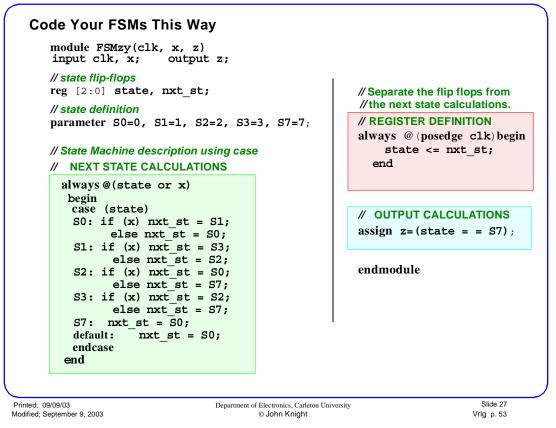

### Standard Form for a Verilog FSM // state flip-flops reg [2:0] state, nxt\_st; // Separate the registers from // state definitions // the next state calculations. parameter reset=0, S1=1, S2=2, S3=3, // REGISTER DEFINITION always @(posedge clk) begin // State Machine description state <= next\_state NEXT STATE CALCULATIONS // end always @(state or . . . ) special equals coming up soon begin // OUTPUT CALCULATIONS next state = ... output= f(state, inputs) end Printed; 09/09/03 Department of Electronics, Carleton University Slide 26 Vrlg p. 51 Modified; September 9, 2003 © John Knight

### Finite-State Machines (FSMs) -

### **Standard Form for FSMs**

# **Standard Form for FSMs**

### Break FSMs into four blocks

### **State Definitions**

The states must always be of type reg.

The states are normally given meaningful names rather than numbers. There are two common methods:

- 1. Use parameters as shown on the slide.

- 2. Use macros (`define) to do textual substitution when compiling. Synopsys suggests you use `define for global names and parameters for local names.

```

`define reset 0 // Use one `define per line and no semicolon. `define S1 1

```

```

`define S2 2

```

if (x) next\_state =`S1; else next\_state = `S0; //Use a back quote whenever a macro is used.

### Next State Calculations

<u>Registers</u>

```

<u>Outputs</u>

```

### Do It My Way

All Verilog programmers expect finite state machines to be constructed this way. If you mix up these four parts, not only will you have much more trouble debugging your code, but any programmer reading your code will wonder who taught you!

**Generic Code for FSMs**

# **Generic Code for FSMs**

Never never mix the next state calculations in with the flip flop definitions.

### Next State Calculations

It is very common to use a combination of **case** and **if** for this block.

Note the default case handles all the state values not specifically mentioned in the case. If this were not put in then cases for state = 4, 5 and 6 would have to be explicitly mentioned or latches would be generated.

#### **Output Calculations**

Here they were so simple one assign statement could easily be used. No need to write an always block.

**Generic Code for FSMs**

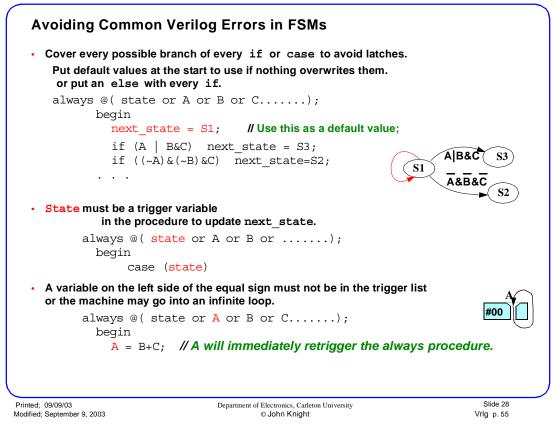

# **Avoiding Common Errors in FSMs**

### **Cover Every Possible Branch**

The alternative to writing over a default value is making the defaults appear in every else.

always @( state or A or B or C.....);

begin

if (A | B&C) next\_state = S3; else next\_state = S1

if ((~A)&(~B)&C) next\_state = S1; else next\_state = S1;

. . .

### State must be a trigger variable

**Avoiding Common Errors in FSMs**

# **Avoiding Common Errors in FSMs**

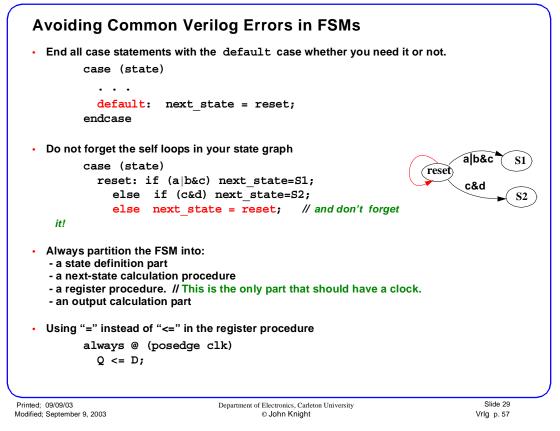

### End all case statements with the default case

Do not confuse the "default case," which is part of the Verilog language, with the "default values" which are often used at the start of an always procedure. See Slide 28

The default case takes care of any cases you forgot and removes a major source of erroneous latches. Your code may be such that some cases never occur. Verilog is unlikely to be able to figure that out and will put in latches anyway unless you use the default.

### Always partition the FSM

Even if you are so smart you can mix up the parts and make it work, the person who tries to maintain your code will be thoroughly confused.

### Using "=" instead of "<=" in the register procedure

The "<=" is the "nonblocking" transfer symbol. (See Slide 41) Not using it will lead to obscure errors when:

1) The same variable appears on both the right and left sides in a procedure.

Q <= Q <<1 // As in this shift register

There are several always @ (posedge clk) registers in the design.

In this case not using the "<=" symbol can lead to races, which are discussed later.</li>

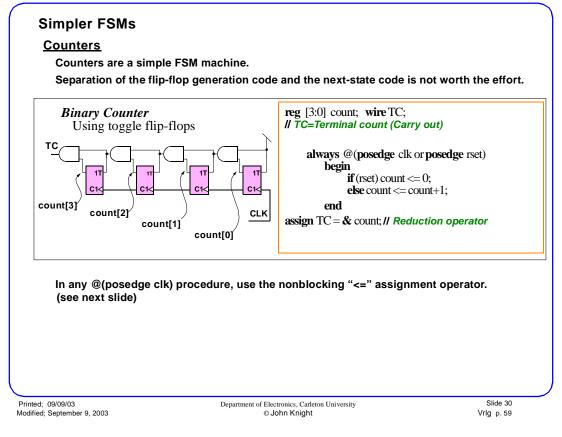

Very Simple FSMs

# **Very Simple FSMs**

# When the Next State Calculation is One Simple Line

For very simple next state calculations we break the rule about separating the next state calculations from the registers.

14.• PROBLEM

```

a. Alternate counter code. Will this synthesize?<sup>1</sup>

always @(posedge clk or posedge rset)

begin

count <= count+1;

if (rset) count <= 0;

end

b. What does this code segment do?

reg [7:0] numb;

always @(posedge clk or posedge rset)

begin

if (du) numb = numb + 8'hff;

else numb = numb + 1;

if (rset) numb <= 0;

end</pre>

```

<sup>1.</sup> a) From what you know now, it would. Check out Slide 38 to see the problem. b)Check out 2's compliment numbers.

Simple FSMs (cont)

# Simple FSMs (cont)

We break the separation rule again.

15.• PROBLEM

In a right shift with two's complement numbers, the most significant bit replicates itself during the shift. Thus 10101 shifted right once becomes 11010. This is called sign extension.

Revise the right shift code below to give the correct answer for two's complement numbers.

```

reg [7:0] Q

always@(posedge clk or posedge rset)

begin

if (rset) Q <= 0;

Q <= Q >> 1;

end

```

| Logic Inference                                                                                    |                                                        |       |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|

| Deciding what logic<br>always @ can infer:<br>flip-flops,<br>latches, and/or<br>combinational logi | to synthesize from code is called <i>infere</i><br>ic. | ence. |

| Flop-Flops                                                                                         |                                                        |       |

| always @(posedge                                                                                   | Clk)                                                   |       |

| This is the stateme                                                                                | ent that tells the logic compiler to generate flip f   | lops. |

| Latches and Combin                                                                                 | national                                               |       |

| always @(C or D)                                                                                   |                                                        |       |

| <ul> <li>This may generate<br/>It may give just con</li> </ul>                                     |                                                        |       |

| <b>Combinational</b>                                                                               |                                                        |       |

| <ul> <li>If any input change</li> </ul>                                                            | e causes a recalculation of all outputs.               |       |

| Latches                                                                                            |                                                        |       |

| <ul> <li>For any output whi</li> </ul>                                                             | ich is not recalculated for all possible input cha     | nges. |

|                                                                                                    |                                                        |       |

### Logic Inference -

**Generating Logic From Procedures**

# **Logic Inference**

# **Generating Logic From Procedures**

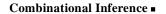

A major concern is that synthesized logic and simulation both yield the same result. This is certainly not always true. Three examples that sometimes do not match are:

- 1. One has an incomplete trigger list but does not generate a latch. See Comment on Slide 33.

- 2. The use of functions which never infer latches.See Slide 35.

- 3. Assigning the same variable in two different procedures. See Slide 45.

### **Incomplete Trigger Lists**

# **Incomplete Trigger Lists**

### What happens

The *Design Compiler* from Synopsys<sup>™</sup> generated an AND-OR gate here as specified. My theory is that because the gate was so explicitly expressed it decided to generate it without the latch.

Other synthesizers might put in latches.

One synthesis engine, no longer available, made a logic block which returned a constant Y=0.

### Moral

Put all the input variable in the trigger list unless you are trying to build latches.

Input variables are:

all variables on the right-hand side of the equal sign,

all control variables for if and case.

### Inserting Latches With or Without Your

### **Combinational Inference** -

**Incomplete Trigger Lists**

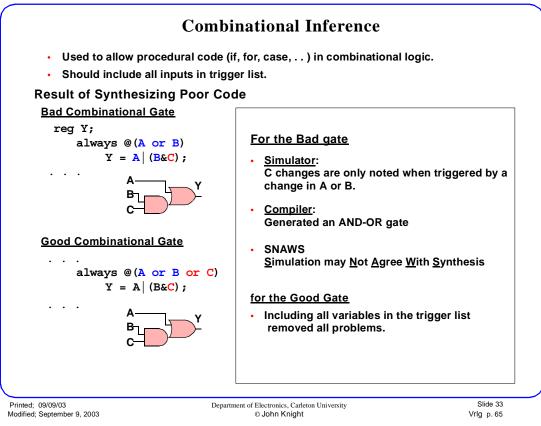

### Latch Insertion in Combinational Ifs

- Latches are inserted if the **else** branch is not explicitly stated. This is a very common error.

- The easy way to make sure all else cases are covered is to assign a default value to all outputs at the start of the procedure. Then use the *if* statements to overwrite it.

| atch Inference from case                                                                                        | These are undefined cases                                                                     |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| // decimal-decoder                                                                                              | 4'h0: Z=0000000000;<br>4'hb: Z=0000000000;                                                    |

| wir [3,0] in;                                                                                                   | 4'hc: Z=000000000;                                                                            |

| reg [10:1] Y;                                                                                                   | 4'hd: Z=000000000;                                                                            |

| always @(in)                                                                                                    | 4'he: Z=000000000;                                                                            |

| case(in)                                                                                                        | 4'hf: Z=000000000;                                                                            |

| 4'h1: Y=0000000001;<br>4'h2: Y=0000000010;<br>4'h3: Y=0000000100;<br>4'h4: Y=0000001000;<br>4'h5: Y=0000010000; | lf one occurs Z will stay at its<br>previous values.<br>Thus synthesis will infer 10 latches. |

| 4'h6: Y=0000 <b>1</b> 00000;                                                                                    | <u>To avoid latches</u>                                                                       |

| 4'h7: Y=0001000000;                                                                                             | Either include all cases,                                                                     |

| 4'h8: Y=001000000;                                                                                              | or equivalently use                                                                           |

| 4'h9: Y=0 <b>1</b> 00000000;                                                                                    |                                                                                               |

| 4'ha: Y= <b>1</b> 00000000;                                                                                     | 4'h9: Y=010000000;                                                                            |

| endcase                                                                                                         | 4'ha: Y=1000000000;                                                                           |

|                                                                                                                 | default: Y=000000000;                                                                         |

|                                                                                                                 |                                                                                               |

Latches Generated When Case is Not Full

# Latches Generated When Case is Not Full

# Full Case

A full case is when an output is specified for all  $2^N$  cases. Where N is the number of bits in the case control.

If the case is not full, latches will be generated, even the unspecified cases can never happen.

16.• Problem

Suggest another method of avoiding latches in a non-full case without using default. Hint, put in a value that will be overwritten.

### **Inserting Latches With or Without Your**

# **Combinational Inference**

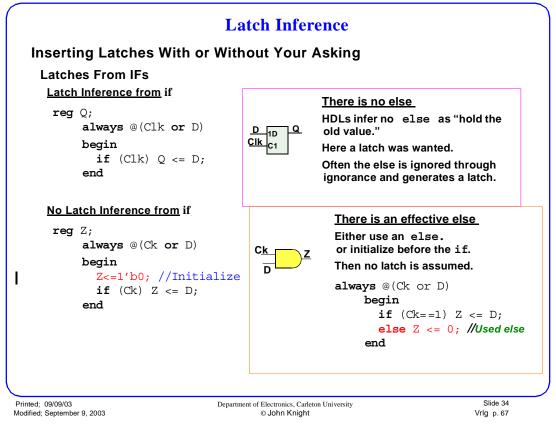

Synthesis of Latches

# **Synthesis of Latches**

Synopsys has trouble telling what an asynchronous reset is for latches.

The Verilog code given does not seem to be enough to tell it to look for a standard cell with an asynchronous reset input.

// Synopsys async\_set\_reset "rst"//

is needed to tell it to find the right standard cell.

### A handy way to write repetitive code.

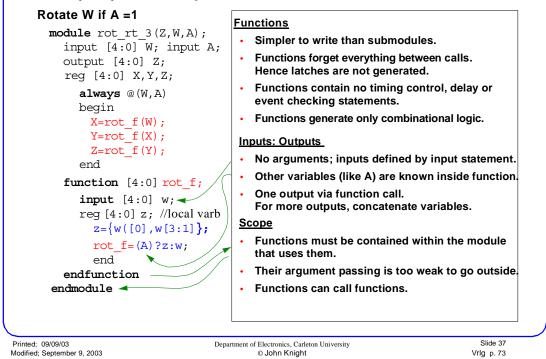

# **Functions**

# A handy way to write repetitive code.

### **Combinational Inference**

### Functions

### **Functions**

### Use functions for clarity and to save writing

- A function can be used to define a block of code which will be repeated.

- 1. It is clearer and shorter than typing multiple detailed copies.

- 2. It is a little simpler than using submodules:

- a. The call is slightly easier to read.

- X=rot\_f(W); seems a little clearer to me than rot\_m rot1(X,W);

- b. A reader, seeing a function, knows immediatelly it is only combinational logic. This is not known for a submodule without checking.

- c. Variable definitions are simpler:

- Out put is defined in function definition line.

function [3:0] rot\_f(W);

- Variables not passed by arguments declared outside the function, are known by the function. See "A" below, used in rot\_f on the slide.

- $rot_f = (A)$ ? w: z; // A defined outside the function.

- Reg type variables, declared outside the function, are known inside the function and can be changed inside the function. See "B" below.

- reg B, function fun1(W); input w; begin  $B=\sim w$ ; ... endfunction.

- Local variables can be defined inside the function when needed. See "z" below, used in rot\_f on the slide.

reg [3:0] z; // defined in the function and not known outside the function..

• The order of arguments in the function input statement must be the same order as in the invocation. x=funl(A,W,B); ... function fun; input a; input [3:0] w; input b; ...

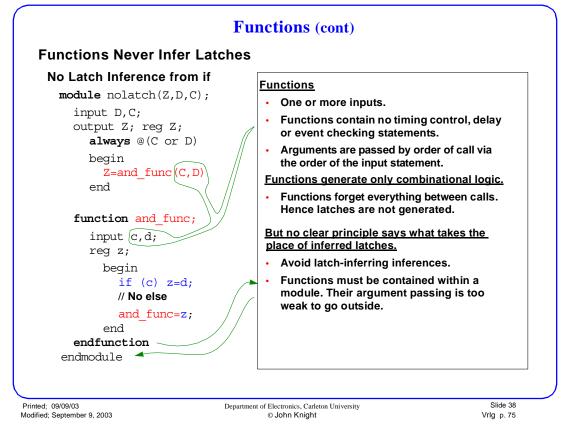

# **Functions Never Infer Latches**

**Functions Never Infer Latches**

### **Combinational Inference** -

| Functions Never Infer Latches                                            | D                          | C·D            | C⊕D | $D + \overline{C}$ | Z=D              |

|--------------------------------------------------------------------------|----------------------------|----------------|-----|--------------------|------------------|

| An incomplete specification                                              |                            | 0 0            | 10  | 1 1                | 0 1              |

| The lack of an else leaves two squares in the<br>Karnaugh map undefined. | 1 0 1                      | 0 1            | 0 1 | 0 1                | 0 1              |

| The possible combinatorial alternatives are:-                            | two squares<br>unspecified | The one chosen |     |                    | Minimal<br>logic |

| $Z=C\cdot D$ , $Z=C\oplus D$ , $Z=D+\overline{C}$ , or $Z=D$ .           |                            |                |     |                    | U                |

#### The and function shown was sent through the Design Compiler, and it generated an AND gate.

It did not generate the simplest logic treating the unspecified cases as don't cares. That would give Z=D. It did treat the unspecified cases as zero which gives  $Z=C\cdot D$ .

### Functions subject to SNAWS<sup>1</sup>

Until a definite principle is generally known, assume anything may come out of the unspecified case.

### Tasks

Task are like functions but can contain multiple outputs and timing information, but not @(posedge clk). Tasks are not treated in these notes or by most synthesizers.

<sup>1.</sup> Simulation does Not Agree With Synthesis

### **Combinational Inference**

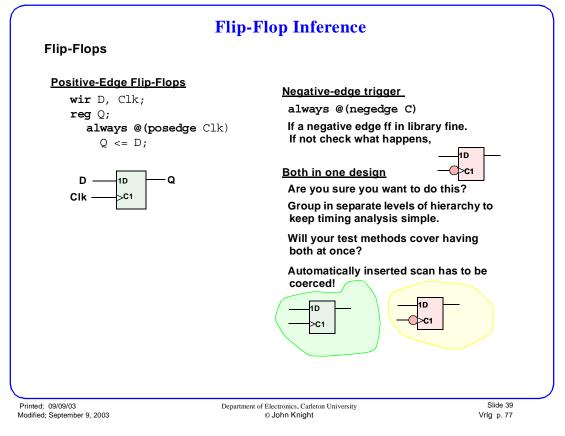

### **Flip-Flop Inference**

# **Flip-Flop Inference**

### **Negative Edge Trigger**

Many libraries do not have falling-edge triggered flip-flop. The synthesizer may then insert an inverter in the clock line. Unless the circuit is all falling edge triggered, this will cause clock skew, and the synthesizer will then insert inverters in the data lines to fix hold time violations.

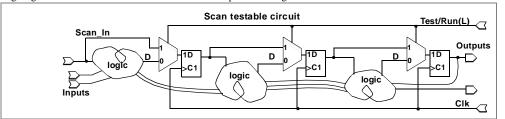

### Scan Testing

Scan testing is a very common test system. The flip flops all have muxs connected to their inputs. When Test/ Run = 0 the circuit runs normally. When Test/Run = 1, the flip-flops are all connected as a shift register. The shift register makes it very easy to set the flip-flops to any values. Then Test/Run is set to 0 to inject these values into the logic and perform a test on the logic.

If some of the flip-flops are falling edge triggered, then one needs two scan chains (shift registers) and the tests going between the chains are at best difficult for present test generation software.

### Why Mix Clock Edges

A few circuits, like RAMbus, use both clock edges. Conversion from these inputs could use one or two opposite edge flip-flops although it is simpler to use latches. Other uses, such as eliminating hold time violations in shift registers, usually have better fixes.

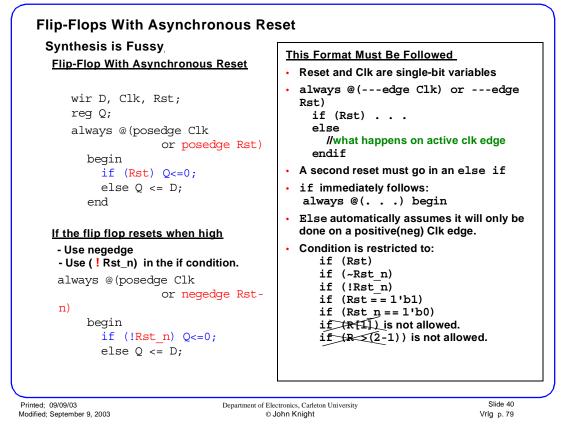

### **Flip-Flops With Asynchronous Reset**

# **Flip-Flops With Asynchronous Reset**

Synthesis assumes that anything with @(posedge...) is a flip flop and does not leave any freedom for creative coding.

```

17.• PROBLEM

always @(posedge clk or posedge rst or posedge set)

if (rst&(~set)) state<=start;

elseif (set) state<=4'hf;

else begin

state<=nxtstate;

end</pre>

```

What is wrong with the above for synthesis?

| <u>Typical Synch Reset Code</u>                                                                     | <ul> <li>Leave off the or posedge Rst.</li> <li>The if - else could be replaced by:<br/>Q&lt;= (!R)&amp;D</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>reg Q; always @(posedge Clk)     begin     if (Rst) Q&lt;=0;     else Q &lt;= D;     end</pre> | <ul> <li>Synchronous resets are easy, but-<br/>They are not as good as asynchronous resets.</li> <li>1. They have setup and hold times</li> <li>2. Be careful using them for "power up" reset<br/>a. The reset signal may violate the setup<br/>time.</li> <li>b. Machine will end up half in the reset<br/>state, and half in state one.</li> <li>3. If clock dividers are reset,<br/>the flip flops they feed may never see<br/>the reset.</li> </ul> |

**Flip-Flops With Asynchronous Reset**

# **Flip-Flops with Synchronous Reset**

These have much more freedom for coding but are less useful.

#### Awkward properties of resets

When applying a synchronous reset, one must be sure that all the flip flops to be rest are supplied with at least one active clock edge during reset. If some flip flops are supplied from a clock divider, and the flip flops in the divider are reset, then divided clock will never appear during reset. This is a disadvantage of synchronous reset.

Asynchronous reset is like any other asynchronous signal. When it changes on the clock edge, some flip flops will get the old value and some the new. This means some of the flip flops will stay in reset another cycle, and the others will come out of reset now. To avoid this one must synchronize the reset signal, that is pass it through a D flip flop before applying it to the other flip flops.

In general the best reset is applied asynchronously and removed synchronously. However the synchronization is done to the reset signal. The individual flip flops still use an asynchronous reset.

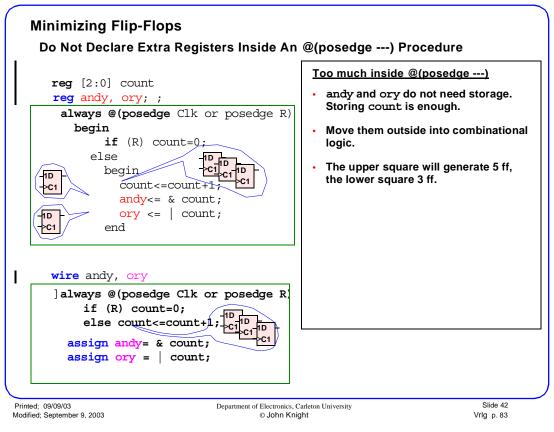

### **Minimizing Flip-Flops**

# **Minimizing Flip-Flops**

The concept is very simple. Partition your finite state machines and do not include outputs in the block which is only supposed to contain registers.

18.• PROBLEM

```

What would you have done differently if you had written the code below.<sup>1</sup>

always @(posedge clk or posedge rst)

if (rst) state<=start;

else begin

state<=nxtstate;

nxtstate= state & (x^y);

end</pre>

```

<sup>1.</sup> Mixing "=" and "<=" won't synthesize. nxtstate will be stored when it should not be.

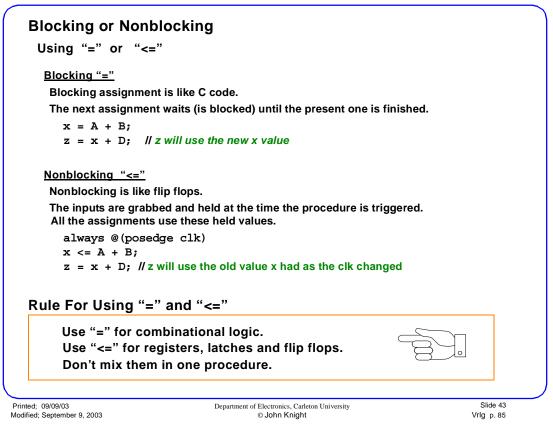

**Blocking and Nonblocking**

# **Blocking and Nonblocking**

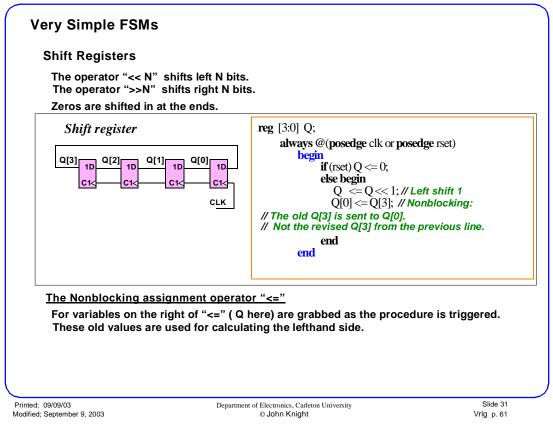

### Nonblocking

In synthesis nonblocking will act as though all right-hand variables were sampled on procedure entry Even for variables calculated within the procedure.

### Example

always @(a or b or c) b<=a; if (b) // will be the old b

#### **Blocking**

Blocking means calculations for the next statement are blocked until the present statement is completed.

initial begin

#1 e=2;

- **#1 b=1;** // completed at t=2

- #1 b<=0 // completed at t=3. A previous blocking statement delays both blocking and nonblocking.

e<=b; // completed at t=3; the preceding statement is nonblocking so this grabbed the old b=1.

f=e; // completed at t=3, using the old e=2. It did not wait for e<=b to complete.</pre>

#### **Rule for Synthesizable Procedures**

Use blocking "=" for all combinational logic.

Allows assignments to depend on previous assignments like C code does.

Use nonblocking "<=" for flip-flops and registers.

Blocking behaves like D-flip-flops, transferring all data simultaneously.

Use nonblocking after always@(posedge clk) in synchronous test benches.

| <u>Shift Registers</u>                                                                       | The Nonblocking Assignment "<="                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wir Clk, X;<br>reg Z,Y;<br>always @(posedge Clk)<br>begin Z=Y; Y=X;<br>end Cl<               | <ul> <li>This is like a real flip-flop.<br/>On the clock edge,<br/>the old outputs are grabbed and use<br/>as the right-hand side inputs.</li> <li>The outputs are all revised based on<br/>these grabbed inputs.</li> </ul> |

| always @(posedge Clk)<br>begin<br>Y=X; Z=Y<br>end<br>But Y is now X<br>always @(posedge Clk) | <ul> <li><u>The Blocking Assignment "="</u></li> <li>Like a C++ program.</li> <li>Statements at the top can change inputs beneath them.</li> </ul>                                                                           |

| begin Z<=Y; Y<=X; C1< C1<                                                                    | ·<br><u>You Can't Use Both</u><br>• Verilog for simulation lets you use a<br>reasonable mix of "=" and "<=."                                                                                                                 |

| always @(posedge Clk)<br>begin <u>Z 10 Y 10 X</u><br>Y<=X; Z<=Y; C1< C1<                     | <ul> <li>Synthesizers will <u>not</u> allow both in one block.</li> </ul>                                                                                                                                                    |

**Blocking and Nonblocking**

# **Blocking and Nonblocking**

### Top Figure

Normal shift register Z=Y; // Z get old Y Y=X; //Y gets input X

### Next Figure Down

$Y{=}X;\,{\prime\prime}/\,Y$  gets input Z=Y;  ${\prime\prime}/\,In\,C$  this would also make Z=X. So does it here.

### **Bottom Two Figures**

Here the values of Y and X are saved when the procedure is entered. Changing Y on the left (output) side does not change it on the input side.