## Scan Tests

#### Scan Tests =

## **Scan Tests**

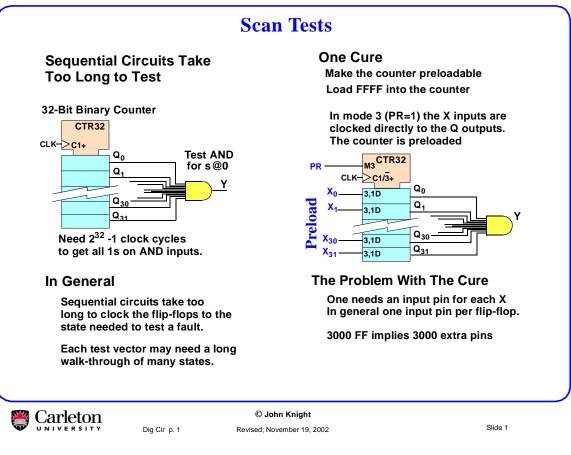

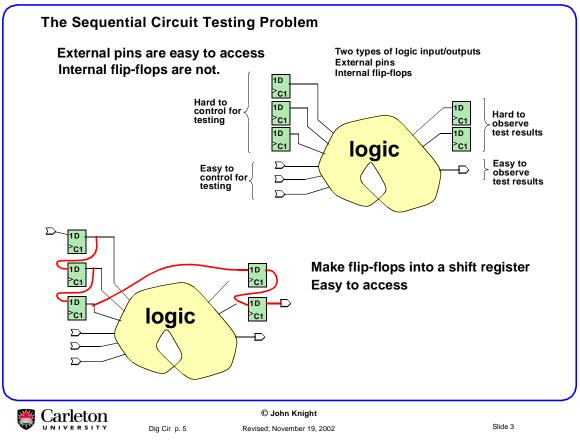

## **The Sequential Circuit Testing Problem**

### To test combinational circuits

One uses a test vector which will give the wrong output if the circuit has a fault. To test for Y, or any  $A_i$ , s@0 one uses test input  $A_0A_1A_2 ...A_9A_{10} = 111...11$

#### To test sequential circuits

One must supply the right inputs <u>and</u> set the flip-flops to the right values to perform the test.

Setting the flip-flops may take many clock cycles. For the 32 bit counter it takes  $2^{32}$ -1 cycles.

#### Symbols

The control signals in the inverted T  $\Box$  at the top of the counter are common to all the flip-flops.

PR is preload. A high PR sets the counter to mode 3 (M3), which is preload. The D inputs (D3,1) load the flip-flops when in mode 3. "3,1" means one needs both mode 3 and an active clock edge represented by "1".

A + on the clock input means a binary up counter.

The "1" on the clock input and some (or all) of the D inputs shows which other inputs are controlled by that clock.

A " $1,\overline{3}+$ " on the clock input means the circuit is a counter from clk1 except in mode 3.

## Scan Tests -

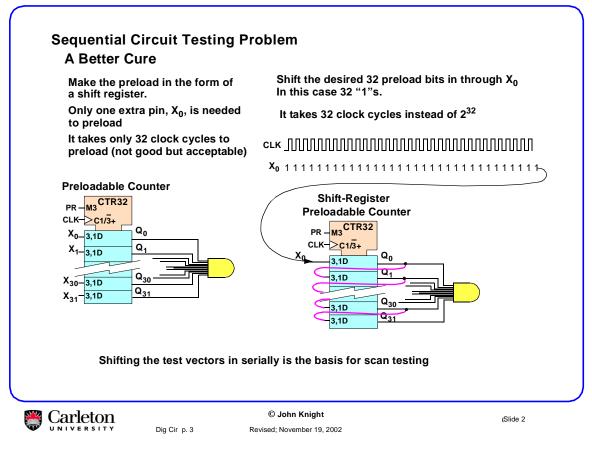

### **Scan Testing**

#### Method

- 1. Convert the flip-flops into a shift register to load in a test vector.

- 2. Load the test vector by shifting the bits through the shift register. This takes N clock cycles. N is the number of flip flops.

- 3. When the vector is loaded, do the test. This takes one clock cycle.

- 4. Convert the flip flops back to a shift register.

- 5. Scan out the results of the test.

- 6. Go back to step 1 and using a new test vector.

Note that scanning in the new test vector is normally combined in the same shifting operation as scanning out the old vectors.

## Scan Tests -

**Concept of Scan Test Test**

## **Concept of Scan Test Test**

## Combinational logic has two types of inputs:

External pins

Outputs of internal flip-flops.

It may be vary hard to set the flip-flops to the desired values to test the combinational circuit. We say the flip-flops have poor controllability.

### Combinational logic has two types of outputs:

External pins

Outputs which go to the D inputs of internal flip-flops.

It is easy to look at the external pins. It may be vary hard to transfer the contents of the flip-flops to external pins. We say the flip-flops have poor observability.

### Scan Tests -

**Basic Scan Test**

## **Basic Scan Test**

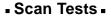

### Test Muxs Added to the Circuit

The original circuit has muxes added in from tof each flip-flop for testing.

The circuit has one to three extra I/O pins

- a. Scan/Run wich changes the sircuit from scan-test mode to normal operation mode.

- b. Scan\_in which is a serial input for test vectors. This may be used as a normal input in Run mode.

- c. Scan\_out which is a serial output for the test results. This may be used as a normal output during Run mode.

## Normal operation

Set Scan/Run to Run.

The muxs disconnect the test shift register.

Circuit becomes the original circuit.

## Scan In/Outt

Set Scan/Run to Scan

Test vectors can be scanned into the flip-flops.

Outputs of the tests on the combinational logic can be shifted out.

## Scan Tests

### Scan Tests -

**Basic Scan Test**

## **Basic Scan Test**

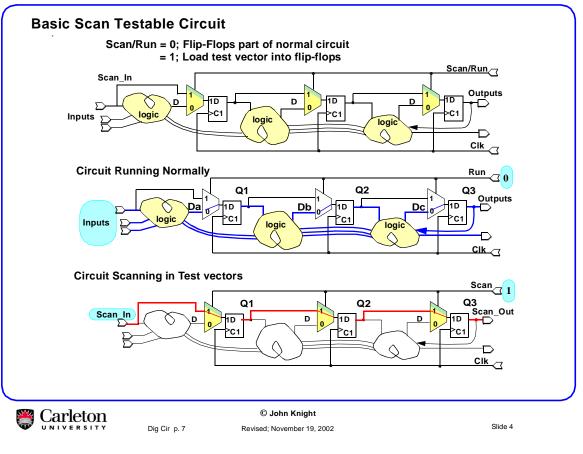

#### Method

1. Switch the MUXs to Scan.

This connects all the flip-flops as a shift register. It disconects the output of the logic blobs from reaching the flip-flop inputs.

- 2. Load the test vector. A test vector, designed to test the logic blocks, is shifted into the flip-flops. This takes as many clock cycles as there are flip-flops in the shift register.

- 3. Switch the MUXs to Run for one clock cycle This reconnects the logic blocks, and makes the circuit run normally for one clokc cycle. The outputs of the combinational logic blobs will appear as:

- a. outputs from the circuit

- b. inputs to the flip-flops (Dx, Dc and Db).

- 4. Clock the combinational logic results into the flip-flops.

- 5. Switch the MUXs to Scan At the same time you will clock out Ta, Db, Dc and Dx and they can be checked for errors.

The data values Tx, Dx, Tc, Dc, Tb, Db, and Ta are shown on the circuit in the positions they would be in just before the clock edge at the end of cycle  $t_4$ .

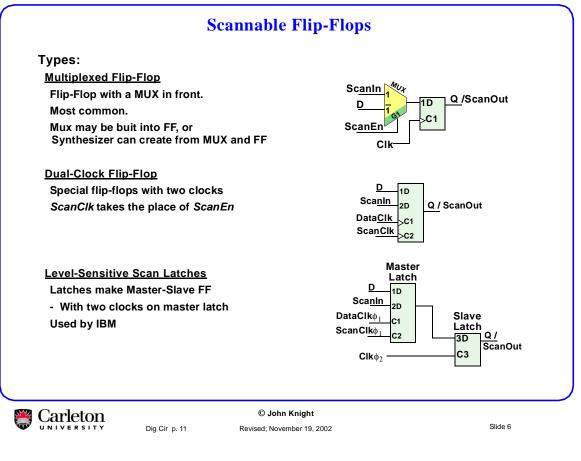

Scannable Flip-Flops

## **Scannable Flip-Flops**

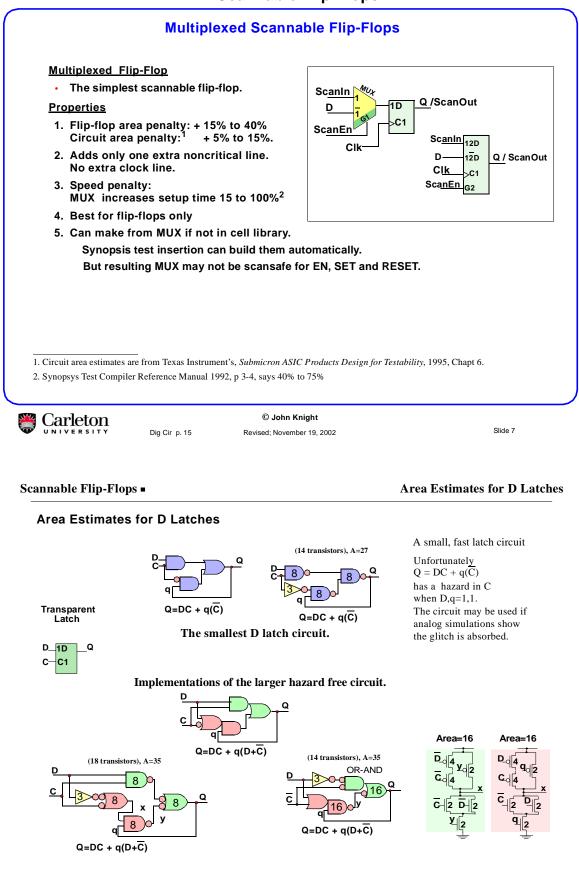

## **Multiplexed Flip-Flop**

- The most common type.

- The synthesizer can construct it from a mux and a normal flip-flop if this cell is not in the library. However it is smaller, faster, and scan-safe (described later) if a special cell is designed.

- Only one noncritical global lead (scan/run) is needed.

- Only one extra pin is needed. Scan\_in and scan\_out can time-share with normal I/O pins.

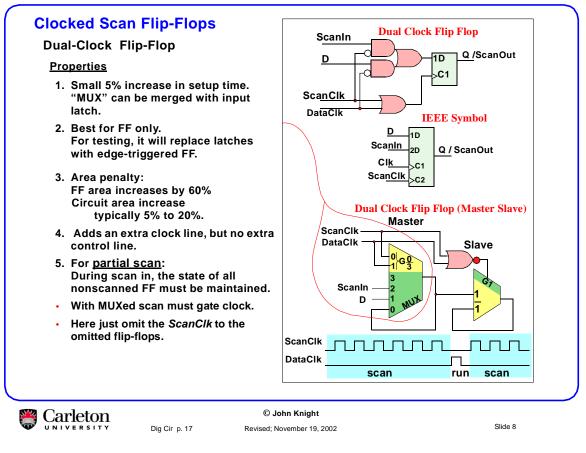

## **Dual-Clock Flip-Flop**

- The fastest scannable flip-flop. It's setup time is only a few percent longer than a normal flip-flop.

- It requires two global leads. Both critical i.e. clocks.

- Best if scan is omitted for some flip-flops (partial scan).

## Level-Sensitive Scan Latches

- Smallest increase in setup time

- · Best for partial scan

- Must route three clocks.

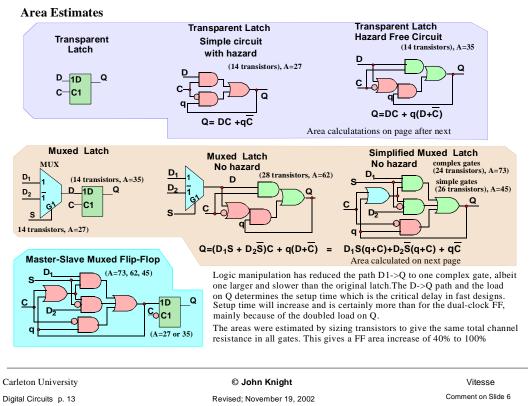

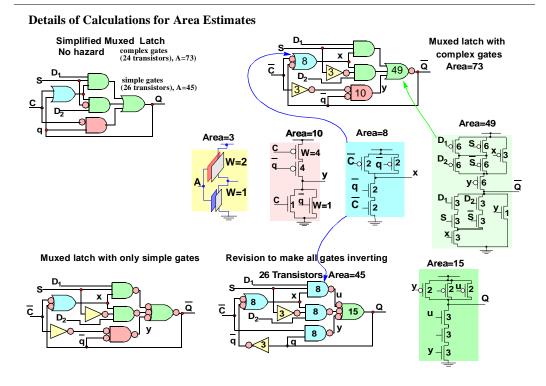

## **Mux Flip-Flop Circuits**

## Scannable Flip-Flops -

## **Mux Flip-Flop Circuits**

Carleton University Digital Circuits p. 14 © John Knight Revised; November 19, 2002 Vitesse Comment on Slide 6

Scannable Flip-Flops -

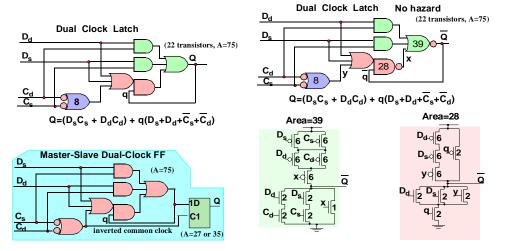

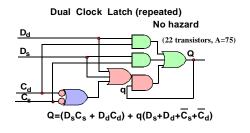

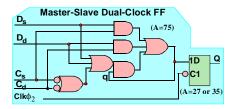

## **Dual-Clock Flip-Flop Circuits** Rough Area and Delay Estimates

Logic manipulation again has reduced the path D->Q to one complex gate not much slower than in the original latch.The load on Q has not increased and the output gate has 3 parallel inputs instead of 2. Setup time will increase little, much less than for the mux FF.

The areas estimates used transistors sized to gave the same total channel resistance in all gates. This gives an area increase of 60% over the nonscanned flip-flop.

**Dual-Clock Flip-Flop Circuits**

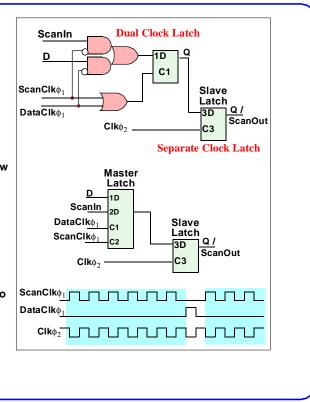

## Level-Sensitive Scan Flip-Flop

### **Properties**

- 1. Good for partial scan.

- With MUXed scan must gate clock.

- Here just omit the scanClk to the omitted flip-flops.

- 2. Level Sensitive has nothing to do with scan. It was what we would now call synchronous design, i.e:

- No gating the clock.

- No using asynchronous reset for logic, only on power up.

- No RS latches, etc.

- 3. Area penalty: FF area increased by 15% to 30% Circuit area increase typically 4% to 20%.

Dig Cir p. 19

- 4. Adds two extra clock lines.

- 5. Small 5% increase in setup time.

## Scannable Flip-Flops -

Carleton

## **LSSD Flip-Flop Circuits**

Slide 9

## **LSSD Flip-Flop Circuits**

The input latch is a dual clock latch, the same as the input latch for the dual-clock flip flop. The second (slave) latch runs from a separate clock.

© John Knight

Revised; November 19, 2002

Some firms, notably IBM, design with an LSSD methodology.

The main use for others, is for partial scan.

Having to route three clocks everywhere is a major drawback.

## LSSD, Rough Area and Delay Estimates

The path D->Q is one complex gate not much slower than in the original latch. Setup time will increase little, but is much less than for the mux FF.

The areas were estimates used transistors sized to gave the same total channel resistance in all gates. This gives an area increase of about 60% over a nonscan flipflop.

| Type of FF                     | FF Area | %incr             | Tsetup*<br>num gates | Tsetup<br>Log effrt | Num Clks/<br>Num Enab |

|--------------------------------|---------|-------------------|----------------------|---------------------|-----------------------|

| FF with no scan                | 70      | 0%                | 2                    | 17                  | 1/1                   |

| Mux + FF                       | 97      | 38%               | 4                    | 37                  | 1/1                   |

| Mux combined with FF, one cell | 80      | 14%               | 2                    | 20                  | 1/1                   |

| Dual-clock FF                  | 110     | <mark>57</mark> % | 2                    | 19.5                | 2/0                   |

| LSSD FF                        | 110     | 57%               | 2                    | 19.5                | 3/0                   |

## Hazard-Free Scan FF Comparison

Area is  $\Sigma W$  taking L=1.

W taken to make all series resistances equal to  $R_{\triangleright\!\!>}.$  Equalizes gate delays for small loads.

Tsetup\* is the number of gates from D to Q-q loop.

W=2 W=1 W=1 W=2 W=2

Other Tsetup is calculated by logical effort.

Dig Cir p. 21

Carleton

© John Knight Revised; November 19, 2002

Slide 10

## Scannable Flip-Flops =

**Comparing Scannable Flip Flops**

## **Comparing Scannable Flip Flops**

#### Area Comparison

The Basic flip flop circuits were optimized and the transistors sized to make the total channel resistance from output to ground, and output to  $V_{\rm DD}$ , the same for all gates.

The flip-flops were constructed from master-slave hazard-free latches.

The area is taken as the sum of the channel areas of all the transistors.

#### Clock-to-Output Times

T<sub>CHQV</sub>was estimated in two ways.

The first way was to count the number of gates that had to be traversed from D to the Q-q feedback loop. This gives a crude estimate that turned out to be surprisingly good, but don't try this with large fanout or fanin.<sup>1</sup>

The second estimates the relative delay from the transistor capacitances as determined by their channel areas.

Neither method includes clock-to-Q delays which will shift delay from setup time to hold time.

<sup>1.</sup> Fanout is the number of gates inputs, or in this case the capacitance, seen by an output driver. Fanin is the number of gate inputs, or more important here, the maximum number of series transistors in the gate .

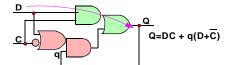

**Special Mux Scan Flip-Flop Properties**

## **Special Mux Scan Flip-Flop Properties**

Enable should be scan safe

<u>Special low drive scan output.</u>

Gated clock built in for partial scan

In the picture shown, the flip flop would be intended to run at least two clock cycles between scans.

## Scannable Flip-Flops -

## The Mux-D Scan Flip-Flop

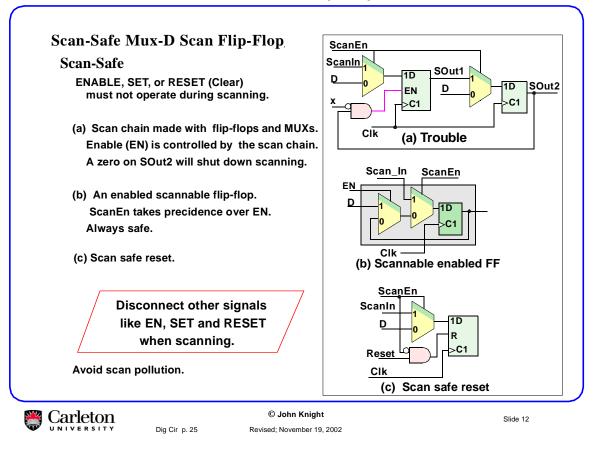

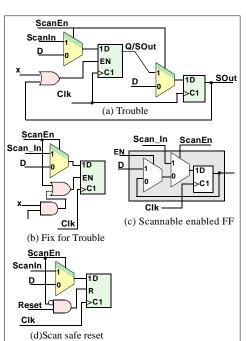

### Scan-Safe

Flip-flops must be immune to all outside influences when the scan chain shift register is operating. If the flip-flop has an enable, set, or reset which takes

priority over the scan commands then one must be sure they never operate during scanning.

#### On the right:

(a) A scan chain made with ordinary flip-flops and MUXs. The enable (EN) is controlled by part of the scan chain and can inadvertently shut itself down.

(b) A hand coded repair that lets ScanEn control the enable.

(c) An enabled scannable flip-flop. It is scan safe. The synthesizer will use them if they are in the library.(d) Scan safe reset.

## The Mux-D Scan Flip-Flop

## Scannable Flip-Flops =

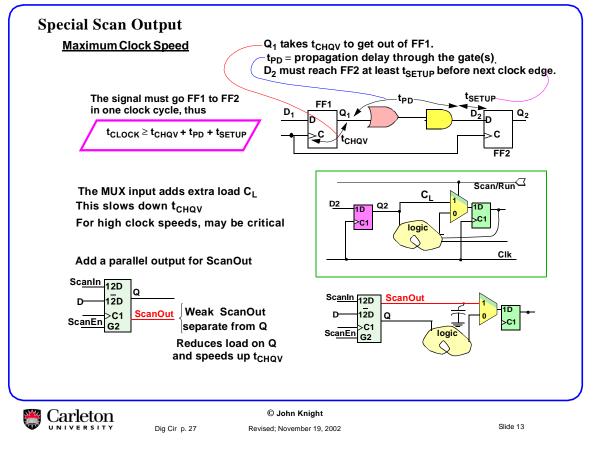

**Special Scan Output**

## **Special Scan Output**

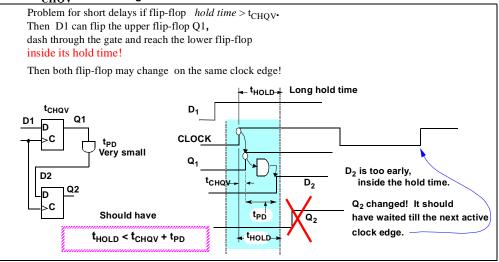

#### Increase t<sub>CHOV</sub> for Shift Registers Scan Chains

Shift Registers have very small  $t_{PD}$  .

Scan circuits are shift registers.

Good to have t<sub>CHOV</sub> slow in shift registers.

Moral: When adding an extra scan output, make it weak and slow.

**Special Scan Output**

scanned

not scanned

scan in

scan er

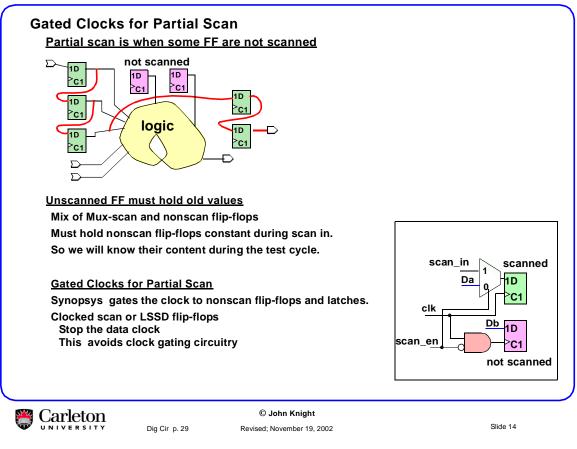

### **Partial Scan**

#### Circuits with some unscanned flip-flops or latches.

Latches are used for skew correction.

Clock dividers have very critical timing and may not want to have scan added. Full-scan may be considered too costly in area or delay,

although partial scan is often considered too complicated.

#### Test insertion programs

They may add add a slave latch to latches. This is unused normally but is used during scan to make the latch into a flip-flop.

For unscanned flip-flops, some test insertion programs gate the clock. This allows the flip-flop to maintain its old value during scan. A better method would be to disable the flip-flop during scan as shown.

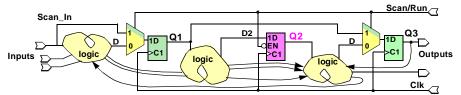

#### Example of a circuit equiped for partial scan

It can: (1) scan in a test vector.

- (2) Run a test which will place a desired value on D2.

- (3) Scan in another test vector to put desired values on Q1 and Q3  $\,$

- (4) Run the this test vector which includes Q2 as an input to the combinational logic.

- (5) Scan out the results.

Carleton University Digital Circuits p. 30 © John Knight Revised; November 19, 2002 Vitesse Comment on Slide 14

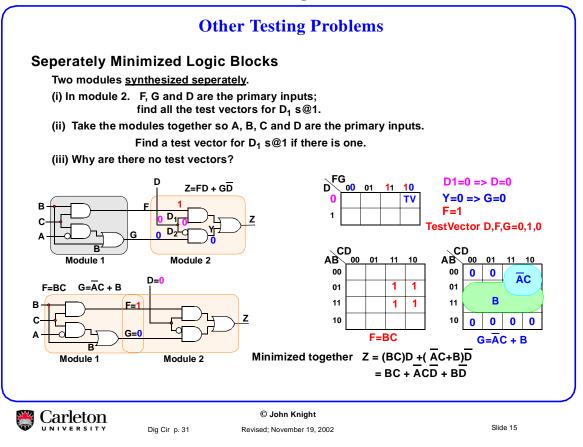

## **Other Testing Problems** -

Finding a Test for D<sub>1</sub> S@1

## Finding a Test for D<sub>1</sub> S@1

## **One Reason For Lower Test Coverage**

When connected logic modules are synthesized separately, the complete circuit may not be minimized. There may be connections fed from the first to the second module which may cause problems.

The logic in module two was synthesized as though all possible combinations could appear on wires F and G. In reality only F,G = 0,0; 0.1; and 1,1 can appear. F,G=1,0 can never be generated by module one.

The test for  $D_1 \le 0$  is trying to test logic for D,F,G= 0,1,0 which can never happen in the combined module. The circuit has extra redundant logic which is never used.

If one minimized both modules together, the minimal sum-of-product's circuit would have been  $Z = BC + \overline{ACD} + \overline{BD}$

This his no redundant logic and would have been 100% testable for single stuck-at faults.

Control

Ea

Control

F≰

Test for slow to rise at D

Obs

Improper test for slow to rise at D Path sensitization changes

A=

B=1 r

C=0

A=

B=1

C

## Faults for At Speed Testing

Transition Delay Faults (Gate Delay Faults) Faults are slow to rise and slow to fall

To test for slow to rise at D.

Force D to 0, same pattern as for a S@1 fault. Wait until the output receives the good value. Change pattern, force D to 1 Keep the path D to F sensitized.

)Do not cause glitches in the path D to F by changing the way it is sensitized.

Delay fault testing always finds s@ faults. These effectively have infinite delay.

ATPG tests are usually generated to be observed on the closest output.

Path delay tests want the longest path.

Dig Cir p. 33

The one most likely to fail by say slightly thin metal. In transition delay faults (gate delay faults) one wants to sensitise a path from the input to the output. ATPG for this is almost the same as for a stuck at fault test.

Carleton

© John Knight Revised; November 19, 2002

Slide 1

Late

rise

=0 Late

rise

**Other Testing Problems** -

Finding a Test for D<sub>1</sub> S@1

Transition Delay Faults (Gate Delay Faults)

# Other Testing Problems

© John Knight Dig Cir p. 35 Revised; November 19, 2002

Slide 1