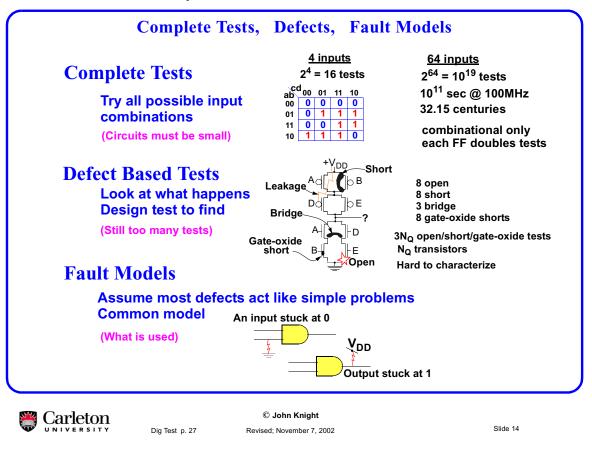

Complete Tests, Defects, Fault Models -

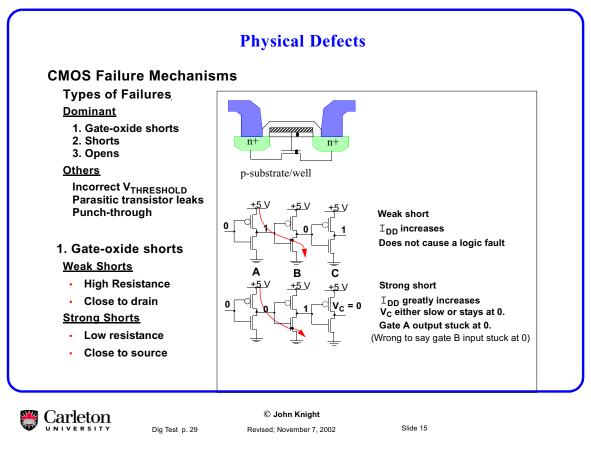

# **Physical Defects**

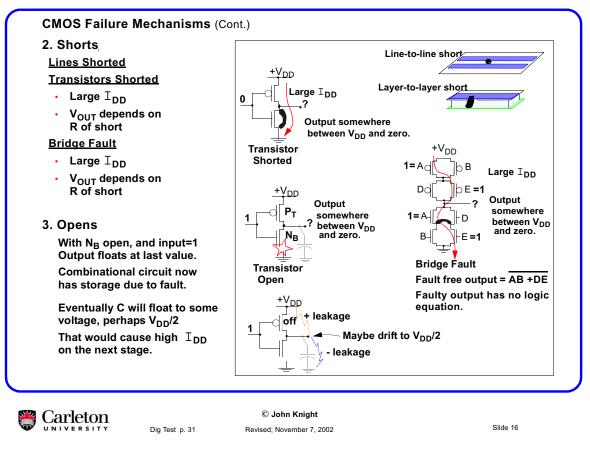

## **CMOS Failure Mechanisms**

#### **Types of Failures**

- Gate-Oxide Shorts

- Shorts

- Opens

- Punch-through: When the source-drain voltage gets too high for the channel length. The high field accelerates electrons so fast they ionize atoms in the channel by impact. This generates more high speed electrons which trigger more ionization. The effect sustains itself and the gate loses control.

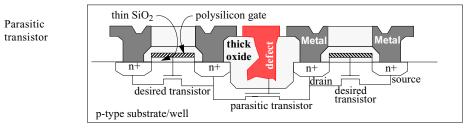

The figure shows two desired transistors constructed between two n+ regions underneath the polysilicon gate. The channel is along the surface of the silicon under the thin SiO2, under the polysilicon gate. The transistors are shown schematically under the drawing showing their construction.

A defect in the thick oxide allows metal to reach almost through the thick oxide. Then part of the thick oxide becomes thin oxide, and may make a weak undesired transistor.

# Physical Defects

### Physical Defects -

## Physical Defects

### Physical Defects -

**Some Fault Models**

## **Some Fault Models**

Some bridge faults may oscillate

- Defects are physical things like gate-oxide shorts.

- Fault models try to model the effects of defects as simple circuit changes.

- Fault models make it easier to see how to test for the defect.

#### Some Fault Models An input stuck at 0 "Stuck At" Models VDD Assumes defects can be modelled as a gate input or output shorted to ground or V<sub>DD</sub>. Very widely used. Output stuck at 1 Often the only model used. **Bridge Fault Models** Assumes defect can be modelled as a wire between gate inputs/outputs. **Bridge Faults** Hard to generate tests. Stuck-Open Faults Gate can only pull one way. Stuck Open Fault Usually found by I<sub>DDQ</sub> tests Slow-To-Rise/Fall Faults Slow gates Long delay Hard to test. Slow-to-Rise Fault © John Knight Carleton Slide 17 Dia Test p. 33 Revised; November 7, 2002

#### Fault Models of Defects -

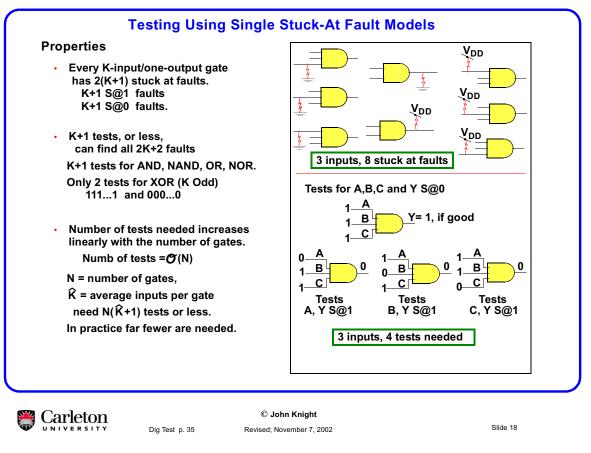

**Testing Using Single Stuck-At Fault models**

## **Testing Using Single Stuck-At Fault models**

One can formally prove that every K input black box needs no more than K+1 tests for single stuck at faults on the input leads, or ouput lead. However one needs more tests if one looks at gates inside the box.

Numb of tests  $= \mathcal{O}(N)$  means the number of tests increases linearly with N.

This is important for large circuits. For example, if the number of tests increased as  $\mathcal{O}(N^2)$  the number of tests for a million gate circuit would increase a million times. It would be not be possible to do such tests!

With an odd number of inputs 2 tests will find any single stuck at fault in an XOR. With an even number of inputs one extra test is needed to check the output for S@0.

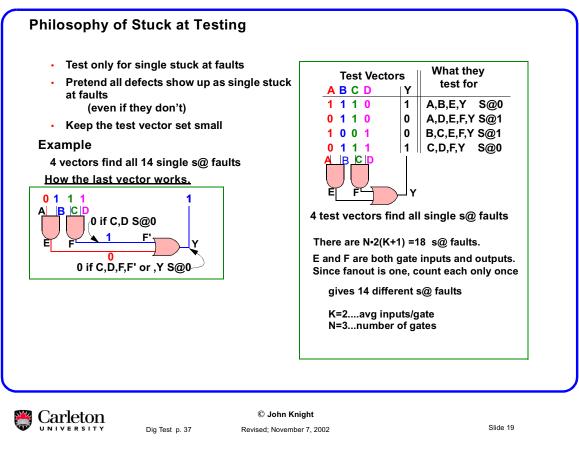

How Stuck @ Tests are Used

## How Stuck @ Tests are Used

Each lead has two faults. Because F and F' are the same lead, removing F' removes two of the stuck-at faults.

Fault Models of Defects •

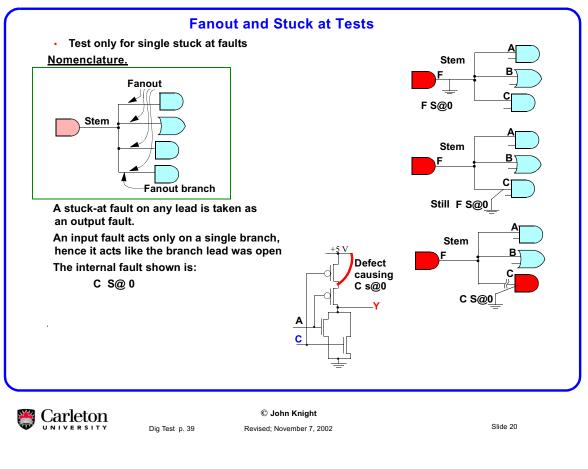

Fanout and Stuck@ Models

Fanout and Stuck@ Models

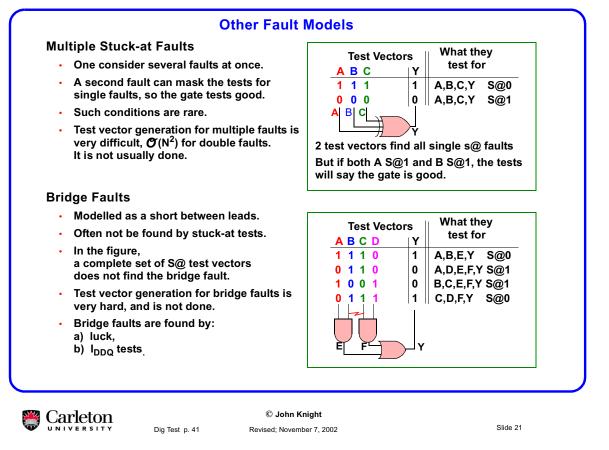

Multiple Stuck@ and Bridge Faults

## Multiple Stuck@ and Bridge Faults

Because it is so time consuming, tests for even double faults are not specifically done. However masking examples like the XOR are very rare. Almost any third test vectors would expose the double XOR fault.

Fault Models of Defects •

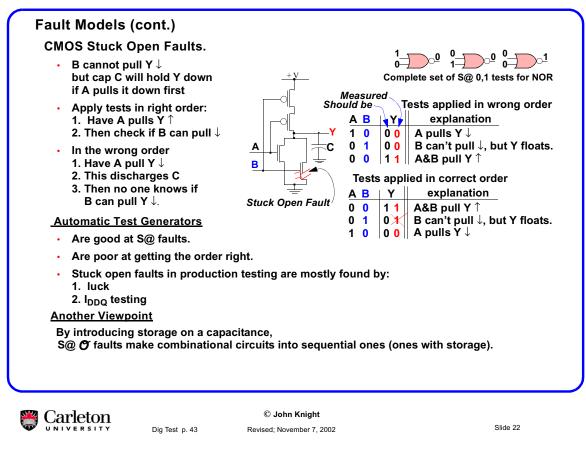

**CMOS Stuck-Open Faults**

**CMOS Stuck-Open Faults**

#### Fault Models of Defects •

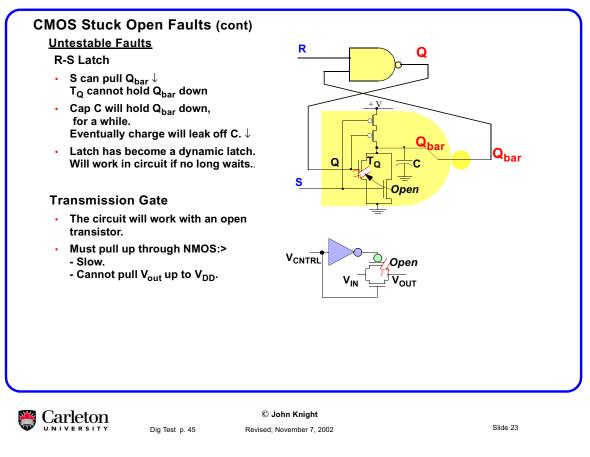

**Untestable Stuck-Open Faults**

## **Untestable Stuck-Open Faults**

#### R-S latch

The latch will work at high and medium speeds because the capacitance will hold  $\overline{Q}$  low for a while. After some time, perhaps 0.1 to 10 ms., the capacitance may discharge and the latch will forget.

This fault is called untestable reasonable production testing methods, because the tester would have to check how long the latch would hold a stored value. The tester must not, while waiting, send out a test vector that would recharge the capacitance. Also it must not send out signals on nearby lines that might capacitively couple energy into the capacitance. It is very very difficult to tell how nearby lines will affect the charge.

#### The transmission gate

A transmission gate with an open transistor will have a high resistance when passing one polarity of signal. In this case, with the PMOS transistor open,  $V_{OUT} < V_{DD}$  -  $V_{Threshold.}$

Also  $V_{OUT}$  will rise only slowly through the PMOS transistor and may give a slow-to-rise fault. Scan tests are usually run at less than full speed, and may not find the fault.

<u>At speed testing</u> may find such faults, but these tests are still far less commonly done than scan testing for stuck@ faults.

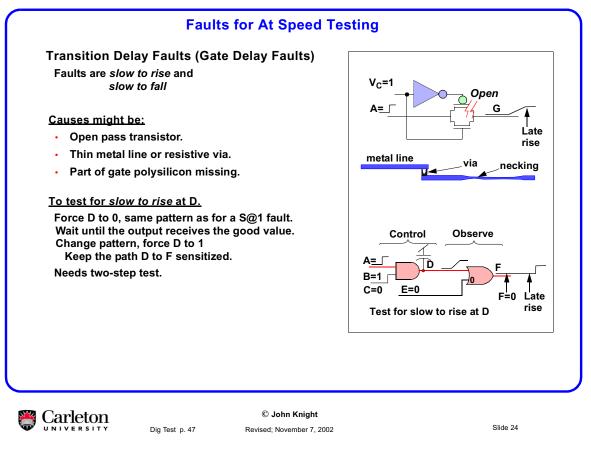

#### Transition Delay Faults (Gate Delay

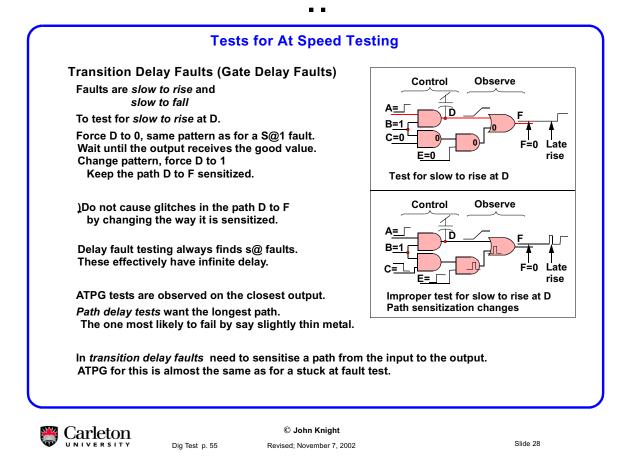

## **Transition Delay Faults (Gate Delay Faults)**

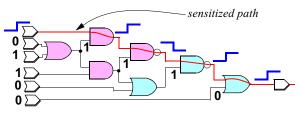

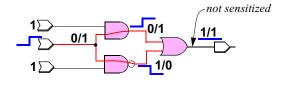

Sensitized Path

In a sensitized path through a circuit,

a single level change at the input to the path causes a change at the path output. Placing different values on the other inputs can desensitize the path.

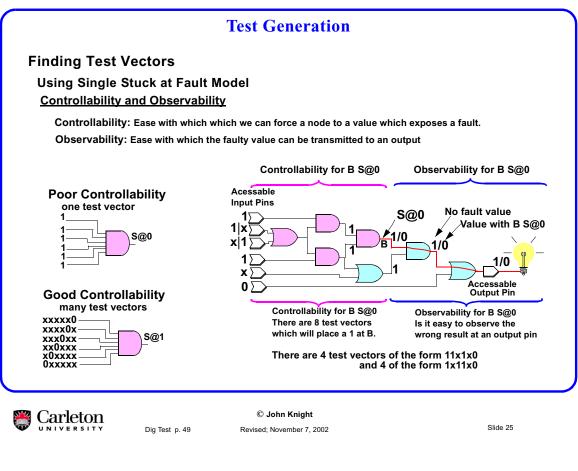

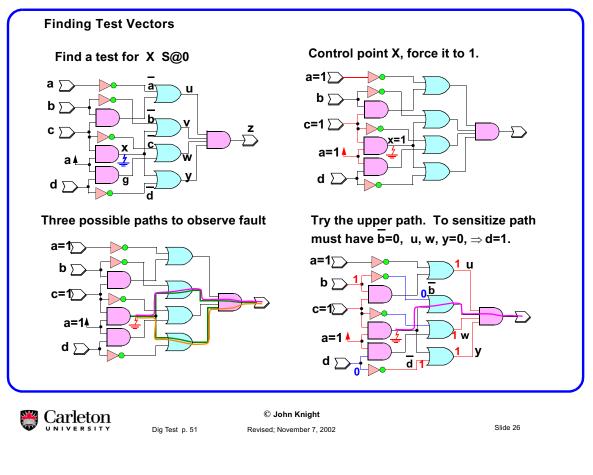

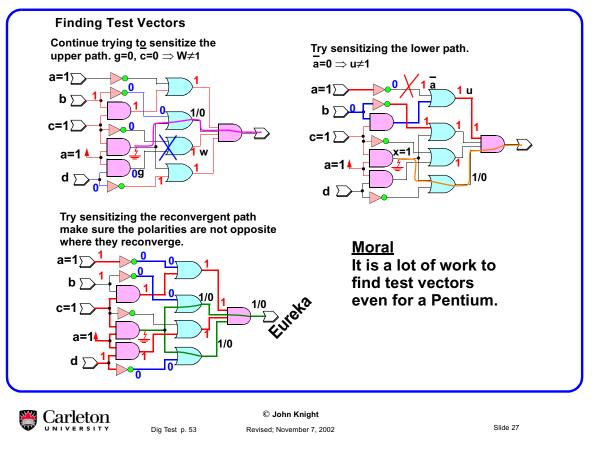

# Test Generation

Test Generation -

**Transition Delay Faults (Gate Delay**

# Test Generation

Test Generation -

**Transition Delay Faults (Gate Delay**

# Test Generation

Test Generation -

**Transition Delay Faults (Gate Delay**

**Tests for At Speed testing**

**Transition Delay Faults (Gate Delay**