# Lab 1: Schematic and Layout of a NAND gate

In lab 1, our objective is to:

- Get familiar with the Cadence Virtuoso environment.

- Draw a schematic of a simple NAND gate and simulate it.

- Draw layout of a NAND gate using cell library, then run a design rule check (DRC), extract, run a layout versus schematic (LVS) and simulate the extracted circuit.

- Compare the schematic and extracted simulations.

In this lab procedure, detailed procedures and snapshots are given for the sake of understanding. You are supposed to understand the procedures, so that you can design your own circuit later. The other lab procedures will not be as elaborate except where necessary. Please refer to this lab procedure in future labs for reference.

#### Login procedure:

After logging in to the computer in the lab using your existing DoE accounts, double click on the "**Unix Systems**" icon to start the remote login server on the Unix machine. Choose one of the computers from the list and click "**Connect**". Ask the TA(s) for help if you have trouble. When you are prompted to enter your username and password, ask the TA(s) for your username and initial password. Make sure you **change your password** as soon as you log in for the first time and **remember** it for the rest of the labs. *The TA(s) might not be able to help you if you forget your password*.

## **PART A: Procedure**

- 1. Open a terminal and create a folder in your home directory for Lab 1 "elec4708/lab1"

- > mkdir elec4708

- > cd elec4708

- > mkdir lab1

- > cd lab1

- Start Cadence in the directory your just created. A window allowing you select the technology kit should popup. Select the TSMC 65nm GP (general purpose) OA technology kit. (Kits ending in OA will open in Cadence 6)

- > startCds

|              | cmc_kits_view                                                   | _ 0 ×        |

|--------------|-----------------------------------------------------------------|--------------|

| <u>F</u> ile |                                                                 | <u>H</u> elp |

|              | A                                                               |              |

| CI           | МС                                                              | search       |

| You          | must be a designer/prototype level subscriber of CMC Microsyste | ms to use    |

|              | To purchase a subscription go to www.cmc.ca or call 613-530-4   | 666          |

| 0            | startCds_ibm130nm.1.8.0.2                                       | A            |

| 0            | startCds_ibm130nm.1.8.0.4                                       |              |

| 0            | startCds_ibm130nm.1.8.0.4_oa                                    |              |

| 0            | startCds_qubic.9.4.a                                            |              |

| 0            | startCds_st65nm.1.0                                             |              |

| 0            | startCds_st90nm.3.0                                             |              |

| 0            | startCds_tezzaron.2010q2v1                                      |              |

| 0            | startCds_tezzaron.2011q2v2                                      |              |

| 0            | startCds_tezzaron.2011q2v2_oa                                   |              |

| 0            | startCds_tezzaron.2011q2v3                                      |              |

| 0            | startCds_tezzaron.2011q2v3_oa                                   |              |

| 0            | startCds_tsmc65nm_gp.1.2                                        |              |

| ۲            | startCds_tsmc65nm_gp_OA.1.2                                     |              |

| 0            | startCds_tsmc65nm_lp.1.5a                                       |              |

| 0            | startCds_tsmc65nm_lp_OA.1.7                                     |              |

| 0            | startCds_tsmc90nm_gp.1.0a                                       |              |

| 0            | startCds_tsmc90nm_gp_OA.1.2                                     |              |

| 0            | startCds_tsmc180nm.5.2                                          |              |

| 0            | startCds_tsmc350nm.4.3                                          |              |

| EL.          | Í                                                               |              |

|              | run                                                             | Quit         |

3. Close the "What's New" window if it appears. The Virtuoso console should still be open.

| C Virt                                                  | uoso® 6.1.4-64b - Log: /home/sukneetbasuta/CDS.log                              | _ = ×    |

|---------------------------------------------------------|---------------------------------------------------------------------------------|----------|

| <u>F</u> ile <u>T</u> ools <u>O</u> ptions <u>H</u> elp |                                                                                 | cādence  |

|                                                         | ROPERTY OF MENTOR GRAPHICS CORPORATION<br>SORS AND IS SUBJECT TO LICENSE TERMS. |          |

| ∏<br>mouse L:<br>1   >                                  | M:                                                                              | Es<br>B: |

4. The next thing we will do is make a library to hold all your work for lab1. Click on **Tools -> Library Manager** (or simply press **F6**). Library manager window should pop up.

|              | Library <u>M</u> anager                    |                                              |         |

|--------------|--------------------------------------------|----------------------------------------------|---------|

|              | Library <u>P</u> ath Editor                |                                              |         |

|              | Verilog Integration                        | •                                            |         |

|              | V <u>H</u> DL Tool Box                     |                                              |         |

|              | Mixed Signal <u>E</u> nvironment           | <ul> <li>International statements</li> </ul> |         |

|              | ADE <u>L</u>                               |                                              |         |

|              | ADE <u>X</u> L                             |                                              |         |

|              | Characterization and Modeling              |                                              |         |

|              | AMS                                        |                                              |         |

|              | <u>T</u> echnology File Manager            |                                              |         |

|              | <u>D</u> isplay Resource Manager           |                                              |         |

|              | A <u>b</u> stract Generator                |                                              |         |

|              | Set Cell T <u>y</u> pe                     |                                              |         |

|              |                                            |                                              |         |

|              | SKILL Development Environment (New)        |                                              |         |

|              | <u>S</u> KILL Development                  |                                              |         |

|              | Con <u>v</u> ersion Tool Box               |                                              |         |

| Č            | <u>U</u> niquify                           | yg: /home/sukneetbasuta/CDS.log              | _       |

| <u>F</u> ile | <u>T</u> ools <u>O</u> ptions <u>H</u> elp |                                              | cādence |

| 77           | OR ITS LICENSORS AND IS SU                 | BJECT TO LICENSE TERMS.                      |         |

|              |                                            |                                              |         |

|              | ing rte.cxt                                |                                              | e       |

| 1            | -                                          |                                              |         |

| ,            |                                            |                                              |         |

| i<br>≣mou:   | se L:                                      | M:                                           | R:      |

| 1   Lik      | orary Manager                              |                                              |         |

## 5. Click **File -> New -> Library**. Type "lab1" in Name field. Click OK.

| Show Categories 🔲 Sho<br>Ibrary                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| iorary                                                                                       | New Library X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| nalogLib<br>asic<br>IsDefTechLib<br>ample<br>baLib<br>mcN65                                  | Library Name Lab1 Directory calculate c4708/tut/ ca |                   |

|                                                                                              | File type: Directories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|                                                                                              | Design Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

|                                                                                              | Use NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| lessages                                                                                     | O Use No DM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| /arning: '/home/sukneetbasut<br>/arning: '/home/sukneetbasut<br>/arning: '/home/sukneetbasut | OK Apply Cancel Help //tcbn8<br>65gplu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65gplus<br>us/TSM |

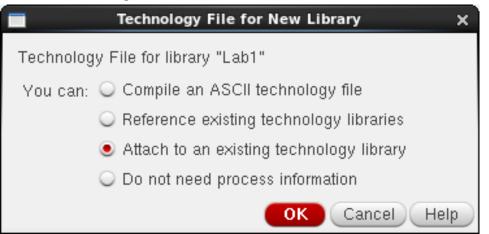

6. Select "Attach to an existing techfile" and Click OK.

7. Select "tsmcN65" from the Technology Library list. Click OK.

| Attach Library to 1 | Technology Library X                                                                       |

|---------------------|--------------------------------------------------------------------------------------------|

| New Library         | Lab1                                                                                       |

| Technology Library  | analogLib<br>basic<br>cdsDefTechLib<br>sample<br>sbaLib<br>tsmcN65<br>OK Cancel Apply Help |

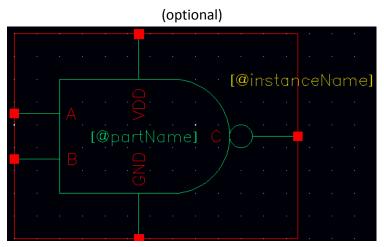

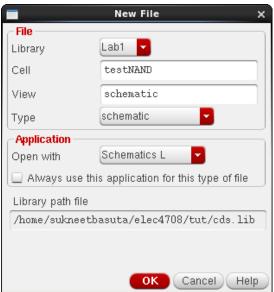

Highlight the new library you have just created, i.e. "lab1", and click File -> New -> Cell View. Type "NAND" in Cell Name. Keep the default values in other fields as shown. Click OK.

|                                                      | Library Manager: Directoryome/sukneetbasuta/elec4708/tut | _ 🗆 X   |

|------------------------------------------------------|----------------------------------------------------------|---------|

| <u>Eile</u> Edit <u>V</u> iew <u>D</u> esign Manager | Help                                                     | cādence |

| Den Ctrl+O<br>Open ( <u>R</u> ead-Only) Ctrl+R       | Library Cell View Category View                          |         |

| Copen With Load Defaults Save Defaults               |                                                          |         |

| Ogen Shell Window Ctrl+P                             |                                                          |         |

| Exit Ctrl+X                                          |                                                          |         |

| Show Categories                                                        |                                                                                                                                                            |            |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| ibrary                                                                 | Cell                                                                                                                                                       |            |

| .ab1                                                                   |                                                                                                                                                            |            |

| ab1<br>analogLib                                                       |                                                                                                                                                            |            |

| asic                                                                   | New File X                                                                                                                                                 |            |

| :dsDefTechLib<br>sample                                                | File                                                                                                                                                       |            |

| sbaLib<br>smcN65                                                       | Library Lab1                                                                                                                                               |            |

| 500005                                                                 | Cell NAND                                                                                                                                                  |            |

|                                                                        | View schematic                                                                                                                                             |            |

|                                                                        | Type schematic                                                                                                                                             |            |

|                                                                        | Open with Schematics L                                                                                                                                     |            |

|                                                                        | Always use this application for this type of file                                                                                                          |            |

|                                                                        | Library path file                                                                                                                                          |            |

|                                                                        | /home/sukneetbasuta/elec4708/tut/cds.lib                                                                                                                   |            |

|                                                                        |                                                                                                                                                            |            |

|                                                                        |                                                                                                                                                            |            |

|                                                                        | OK Cancel Help                                                                                                                                             |            |

|                                                                        |                                                                                                                                                            |            |

| dessages                                                               |                                                                                                                                                            |            |

|                                                                        | נישי סטינטינפטרגווט , בוחפ ס. סמרחטרווחט זוופ ייסואוסיאנטינטונע _סטרוח_ווטטאנט                                                                             | - endleona |

| Varning: '/home/sukneetbasuta/ele<br>Varning: '/home/sukneetbasuta/ele | 2c4708/tut/tech.lib', Line 6: Skipping: '/CMC/kits/tsmc_65nm_libs//tcbn65g<br>2c4708/tut/tech.lib', Line 6: Cannot find file '/CMC/kits/tsmc_65nm_libs//tc | jplus/TSM  |

|                                                                        | c4708/tut/tech.lib', Line 6: Skipping: '/CMC/kits/tsmc_65nm_libs//tcbn65g<br>e/sukneetbasuta/elec4708/tut/Lab1.                                            |            |

9. If a License error pops up like the one below, hit "Always".

| Next License                                                                                                                                                                            | ×          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| (icLic-23) License Virtuoso_Schematic_Editor_L ("95100") is not available to run Schematics Would you like to try checking out the license Virtuoso_Schematic_Editor_XL ("95115") inste | -L.<br>ad? |

| Yes No Always Never Help                                                                                                                                                                |            |

A blank Virtuoso Schematic Editing window will open. Move your cursor through the icons on the top toolbar and pop-up descriptions for each will show up.

| <sup> </sup>                                                       | <u>L</u> aun | ch  | Eil   |      | dit  | ⊻ie  | w   | <u>C</u> re | ate | C | hec | × | Ogt | ions | Mi | grate | <u>v</u> | /jnd | ow  | Cal  | ibre | He   | p  |   |    |    |   |   |     |     |   |    |      | (   |       | enco |

|--------------------------------------------------------------------|--------------|-----|-------|------|------|------|-----|-------------|-----|---|-----|---|-----|------|----|-------|----------|------|-----|------|------|------|----|---|----|----|---|---|-----|-----|---|----|------|-----|-------|------|

|                                                                    | Þ            |     | 8     | 8    | j.   | *    | é   | 9           |     | 1 | ×   | 6 | ) ' | ŗ    | 69 | \$    |          | e    | j.  | Q    | 9    | 6    | Q. | 8 | J. | 망  | 1 | 1 | abc | -10 | Ē |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    | ł. |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      |    |       |          |      |     |      |      |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

|                                                                    |              |     |       |      |      |      |     |             |     |   |     |   |     |      | -  |       |          |      |     |      | -    |      |    |   |    |    |   |   |     |     |   |    |      |     |       |      |

| II mouse L: schSingleSelectPt() M: schHiMousePopUp() R: schHiMouse | mous         | e L | : \$C | hSin | gle: | Sele | C1P | 10          |     |   |     |   |     |      |    |       |          | M: s | chH | iiM0 | useF | PopU | P0 |   |    |    |   |   |     |     |   | R: | schł | HIM | ousei | opUp |

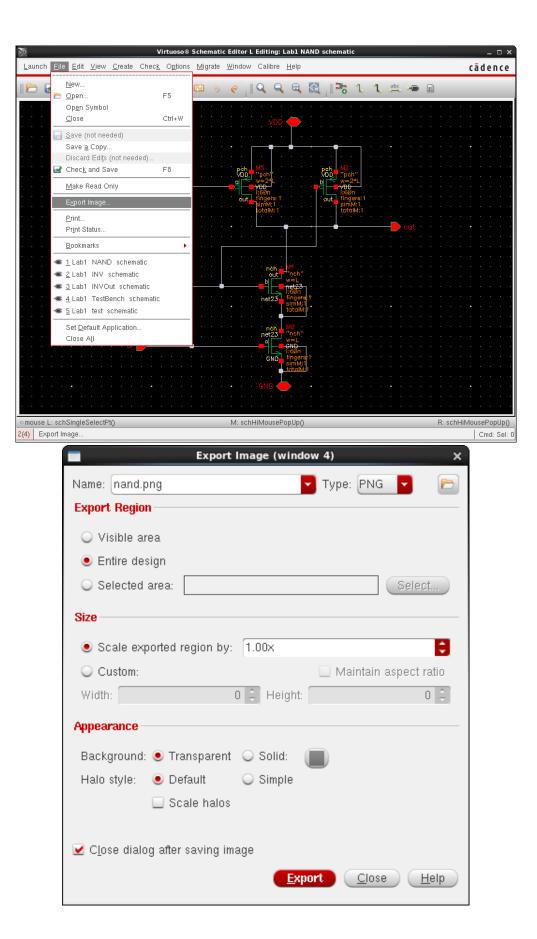

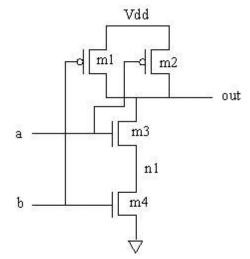

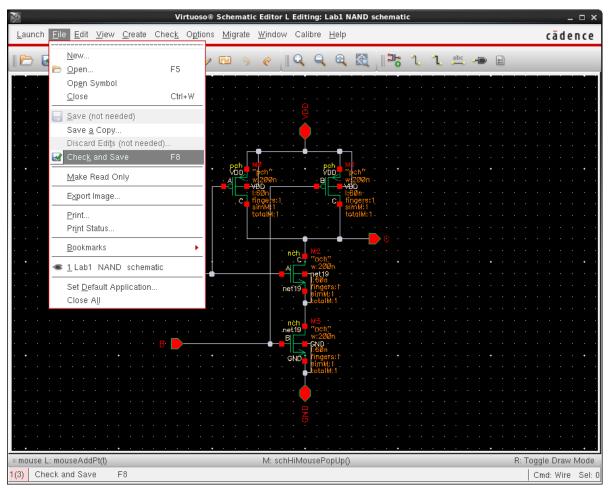

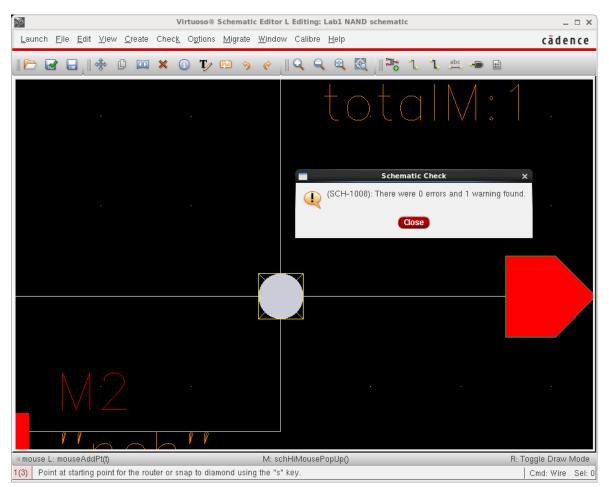

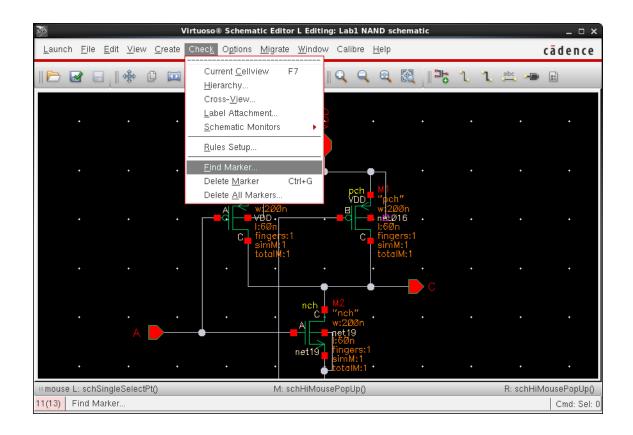

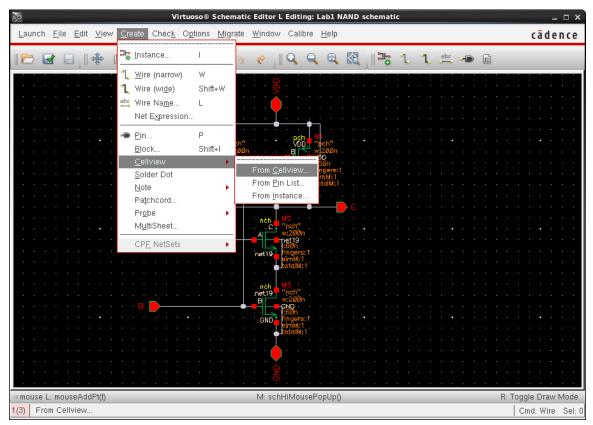

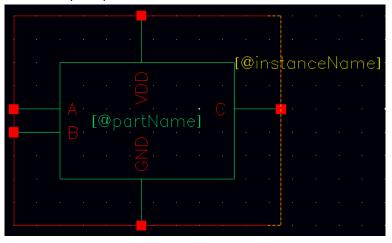

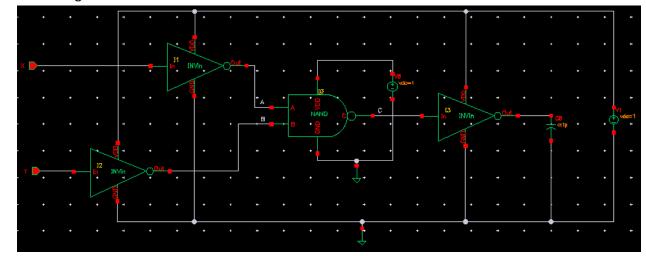

10. The next thing we will do is draw the NAND gate using pfets and nfets. We will also add 2 input pins, 1 output pin, 1 VDD pin and 1 GND pin. A circuit diagram of NAND gate is given here.

11. To add an instance in your schematic, you can click on the Add Instance icon on the top toolbar, or click on **Create -> Instance**, or simply type "i" from the keyboard. The Add Instance dialog box will show up.

| Virtuo                                                                                                                                              | so® Schema          | atic Edito      | or L Editi | ng: La                                | b1 NAN       | D schema       | itic |       |                                       |       |         | >                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|------------|---------------------------------------|--------------|----------------|------|-------|---------------------------------------|-------|---------|----------------------------|

| Launch File Edit View Create Check Op                                                                                                               | tions <u>M</u> igra | te <u>W</u> ind | ow Cali    | bre <u>F</u>                          | <u>l</u> elp |                |      |       |                                       |       |         | cādence                    |

| 🗁 🕢 🕞    🚸 ( <mark>🔭 [</mark> nstance                                                                                                               | I                   | 5 C             |            | Q                                     | Q 🗄          | <u>الا الم</u> | ; 1  | 1     | abc                                   | •     |         | _                          |

| 1, <u>Wi</u> re (narrow)<br>1, Wire (wi <u>d</u> e)<br>2, Wire Na <u>m</u> e<br>Net Expression                                                      | W<br>Shift+W<br>L   | <br>            |            | · · · · · · · · · · · · · · · · · · · | · · ·        |                |      | · · · | · · · · · · · · · · · · · · · · · · · | · · · | · · ·   |                            |

| <ul> <li>✓■ Pin</li> <li>Block</li> <li>Cellview</li> <li>Solder Dot</li> <li>Note</li> <li>Patchcord</li> <li>Probe</li> <li>MultiSheet</li> </ul> | P<br>Shift+I        |                 |            |                                       |              |                |      |       |                                       |       |         |                            |

| CP <u>E</u> NetSets                                                                                                                                 | •                   |                 | · · ·      |                                       |              |                |      |       |                                       | · · · |         | · · · · · ·                |

|                                                                                                                                                     |                     |                 |            |                                       |              |                |      |       |                                       |       |         |                            |

|                                                                                                                                                     |                     |                 |            |                                       |              |                |      |       |                                       |       |         |                            |

| ≡ mouse L: schSingleSelectPt()<br>1(3) Instance I                                                                                                   |                     | M: s            | chHiMou    | usePop                                | )Up()        |                |      |       |                                       |       | R: schH | iMousePopUp()<br>Cmd: Sel: |

- Add Instance tsmcN65 Librarv Browse Cell pch Library Browser - Add Instance View symbol Show Categories Library Cell View Names tsmcN65 symbol pch Array Rows 1 ADVance MS Lab1 pass\_lvt\_mac / Rotate ⊿⊾ Sideways analogLib pass mac ams auCdl basic pcapacitor cdsDefTechLib pch auLvs sample pch\_25 eldoD Model name pch pch\_25\_mac hspiceD shal ih dard WT I description tsmcN65 pch\_25\_macx pch\_25od33 spectre symbol L(M) 60n M pch\_25od33\_mac pch\_25od33\_macx 200n M W (M) pch\_25od33x total\_width(M) 200n M pch\_25ud18 pch\_25ud18\_mac Number of Fingers 1 pch\_25ud18\_macx Multiplier 1 pch\_25ud18x pch\_25x Hide Ca pch\_hvt pch\_hvt\_mac pch\_hvt\_macx pch\_hvtx pch\_lvt pch lvt mac Close (Filters...) Display... (Help)

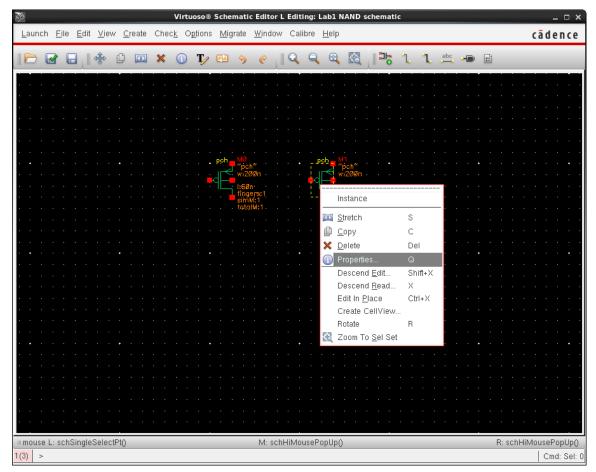

- 12. Click Browse beside Library. Library Manager will pop up.

- 13. In Library, select "tsmcN65", in cell select "pch" (for a pfet device), in view select "symbol". Then click Close.

- 14. Close the Library Browser and, optionally, Hide the Add Instance window. Place the instance in your design. You can place multiple instances of same item, can rotate the instance by typing 'r' on your keyboard, or mirror the instance by hitting "Shift+r". When you are done with placing all the instances of that item, press Esc to leave "Add Instance" mode.

| 8<br><u>L</u> aunc | h E    | ilo  | Edit        | - v      | iouz |      | rea | to | Che  |             |    | oso(         | _        |              | -          | -          |          |     | -   |     |     |           |            | ANC         | ) sci | herr | nati | c | _   | _ |    |          |   |   |   |       |     |     | ād  | -   |     |

|--------------------|--------|------|-------------|----------|------|------|-----|----|------|-------------|----|--------------|----------|--------------|------------|------------|----------|-----|-----|-----|-----|-----------|------------|-------------|-------|------|------|---|-----|---|----|----------|---|---|---|-------|-----|-----|-----|-----|-----|

| Launc              |        | jie  | <u>c</u> un | <u>v</u> | jew  | 9    | jea | le | Cile | :U <u>K</u> | oţ | <u>j</u> uon | 5        | <u>twn</u> é | Jiai       | e          | <u> </u> | 100 | 0   | -   |     | -         | ηų         | _           | _     | _    | _    | _ | _   | _ | _  | _        | _ | _ | _ | _     | _   | C   | a u | er  | 10  |

|                    | R      |      |             | 4Ĵ       | ¢    | C    |     |    | ×    | (           | 1  | Ţ            | <b>,</b> |              | 4          | 5          | ¢        |     |     | 2   | Q   | 6         | 2          | Æ           |       | 12   | 6    | 1 | . ' | 1 | ab | <u>-</u> | - |   | 1 |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    | i.           | Ì        |              |            |            |          |     | Ì   |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     | Ĭ.  |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          | n ob         |            |            |          |     |     |     |     | ob        |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          | PON          | , "        | pch        |          |     |     |     | P   | on        | , "r       | ch"         |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              | C        |              | Ŵ          | 120        | ØN -     |     |     |     | i d | $\square$ | - W:       | 200         |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              | i la<br>fi | 6Øn<br>nae | rs:1     |     |     |     | •   |           | l:E<br>fir | Øn<br>Igers | 3:1   |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          | ·            | si         | mM<br>tal  | :1       |     |     |     |     | •         | si         | ńМ:         |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            | aculi      | 1 - I -  |     |     |     |     |           | . (0       | ean M       |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

| •                  |        |      |             |          |      | •    |     |    |      |             |    |              | •        |              |            |            |          |     |     | •   |     |           |            |             |       |      | •    |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

|                    |        |      |             |          |      |      |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     |           |            |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     |     |     |

| nouse              | e L: s | chSi | ngle        | eSel     | ect  | Pt() |     |    |      | _           |    |              |          |              |            |            | M:       | sch | HiN | 1ou | seP | opL       | lp()       |             |       |      |      |   |     | _ |    |          |   |   | F | ): sc | :hH | iMo | use | Pop | oUp |

| ) >                |        |      |             |          |      | -0   |     |    |      |             |    |              |          |              |            |            |          |     |     |     |     | 1.        | 1.0        |             |       |      |      |   |     |   |    |          |   |   |   |       |     |     |     | nd: |     |

15. You can access the object property window by right-clicking on an instance and selecting properties. Alternatively, you can select an instance and press "q".

16. The Edit Object Properties window will pop up and will show properties of that instance. You can change length or width if required. For now, we will use default widths for pfets and nfets. However, you can change widths later to enhance performance. Note that the default length value is set to the minimum allowed by the technology, but this is not the case for the default width value. **NOTE: It is okay if the width rounds to the nearest multiple of 5.** Due to process variations, there is a limitation on accuracy.

|                         | Edit Object Properties        | 2       |

|-------------------------|-------------------------------|---------|

| Apply To Only curre     | ent 🔽 instance 🔽              |         |

|                         | user 🗹 CDF                    |         |

|                         |                               |         |

| Browse                  | Reset Instance Labels Display |         |

| Property                | Value                         | Display |

|                         | tsmcN65                       | off 🔽   |

| Cell Name               | pch                           | value 🔽 |

| View Name               | symbol                        | off     |

| Instance Name           | M1                            | off 🔽   |

|                         | Add Delete Modify             |         |

| CDF Parameter           | Value                         | Display |

| Model name              | pch                           | off 🔽   |

| description             | dard VT PMOS transistor       | off 🔽   |

| L(M)                    | 60n M                         | off 🔽   |

| w (M)                   | 200n M                        | off 🔽   |

| total_width(M)          | 200n M                        | off 🔽   |

| Number of Fingers       | 1                             | off 🔽   |

| Multiplier              | 1                             | off 🔽   |

| total_m                 | 1                             | off 🔽   |

| Hard_constrain          | ⊻                             | off 🔽   |

| Calc Diff Params        |                               | off 🔽   |

| Source_area             | 3.5e-14                       | off 🔽   |

| Drain_area              | 3.5e-14                       | off 🔽   |

| Source_periphery_(M)    | 750n M                        | off 🔽   |

| Drain_periphery_(M)     | 750n M                        | off 🔽   |

| NRS                     | 0.5                           | off 🔽   |

| NRD                     | 0.5                           | off 🔽   |

| Calc SA SB SD           |                               | off 🔽   |

| SD(Fingers_Spacing)_(M) | 200n M                        | off 🔽   |

- 17. Repeat steps 11. to 14. for the nfets ("**nch**" from the same library) and place them in your design.

- 18. To input and output signals, you need to add pins. To add pins, click on the Create Pin button on the top toolbar, or click **Create -> Pin**, or simply type "**p**" from the keyboard. Add Pin dialog box will open.

| Image: Source       Image: Source         Wire (narrow)       W         Solder Dot       Wolfset         Mote       Wire (narrow)         Pigbe (ndition)       Wire (narrow)         MultiSheet       CPE NetSets         CPE NetSets       Wire (narrow)         Muse PopUp()       M: schHiMousePopUp()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ŵ.                                                   | Virtuoso® Schematic Editor L Editing: Lab1 NAND schematic                                                                                         | _ □ >                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Wire (narrow)       W         Wire (wide)       Shift+W         Wire (wide)       Shift+W         Block       Chille         Solder Dot       Solder Dot         Note       Solder Dot         Prigbe       MultiSheet         CPE_NelSets       VolUk(1)         Note       Solder Dot         MultiSheet       CPE_NelSets         VolUk(1)       KotelMinusePopUp()         Rouse L: schSingleSelecPti()       M: schHiMousePopUp()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u>L</u> aunch <u>F</u> ile <u>E</u> dit <u>V</u> ie | v <u>Create</u> Chec <u>k</u> O <u>p</u> tions <u>Mig</u> rate <u>Wi</u> ndow Calibre <u>H</u> elp                                                | cādence                  |

| 1       Wire (wide)       Shift-W         Wire (wide)       Shift-W         Wire Name       L         Net Expression       Pin         Pin       Pin         Block       Shift-H         Solder Dot       Solder         Note       Patchcord         Prope       MultiSheet         CPE_NetSets       Fragment         MultiSheet       CPE_NetSets         CPE_NetSets       MultiSheet         State       MultiSheet         CPE_NetSets       MultiSheet         R: schHiMousePopUp()       R: schHiMousePopUp()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                    | 1 🔭 Instance I 🥱 🥜 🔍 🔍 🔍 🕄 🔭 1. 1. 🚈 🛥 🖻                                                                                                          |                          |

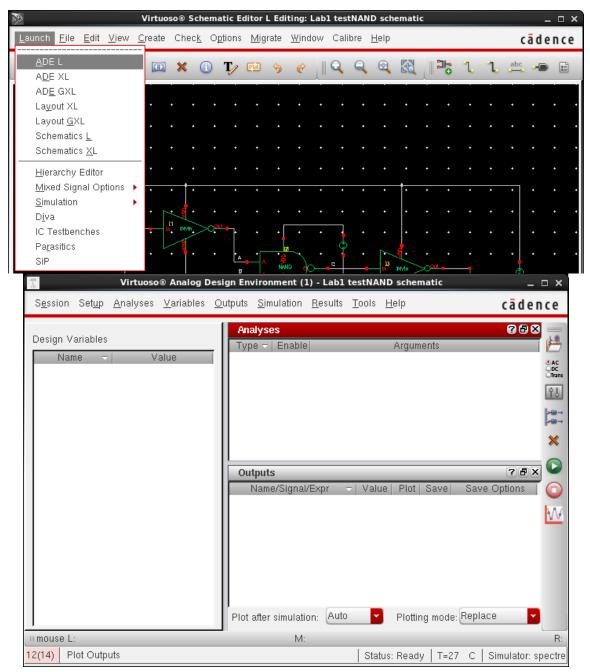

| Block Shift+1<br>Cellview<br>Solder Dot<br>Note<br>Patchcord<br>Probe<br>MultiSheet<br>CPE_NetSets<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>MultiSheet<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets<br>CPE_NetSets |                                                      | 1     Wire (narrow)     W       1     Wire (wide)     Shift+W       1     Wire Name     L                                                         | · · · · ·                |